## **Product Index**

| Bt101 4 - 5       |

|-------------------|

| Bt101/883 11 - 15 |

| Bt102 4 - 19      |

| Bt102/883 11 - 27 |

| Bt103 4 - 33      |

| Bt104 10 - 5      |

| Bt105 10 - 5      |

| Bt106 4 - 47      |

| Bt107 4 - 61      |

| Bt109 4 - 75      |

| Bt110 10 - 17     |

| * Bt208 7 - 5     |

| * Bt251 7 - 21    |

| * Bt253 7 - 41    |

| * Bt261 7 - 65    |

| Bt424 6 - 5       |

| Bt431 6 - 17      |

|   | Bt438 6 - 37      |

|---|-------------------|

| * | Bt438/883 11 - 41 |

|   | Bt439 6-49        |

|   | Bt450 5 - 5       |

|   | Bt451 5 - 19      |

|   | Bt453 5 - 51      |

| * | Bt453/883 11 - 43 |

|   | Bt454 5 - 67      |

|   | Bt457 5 - 19      |

|   | Bt458 5 - 19      |

| * | Bt458/883 11 - 57 |

| * | Bt459 5 - 85      |

| * | Bt460 5 - 131     |

|   | Bt461 5 - 133     |

| * | Bt468 5 - 165     |

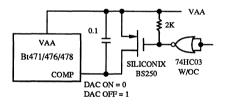

|   | Bt471 5 - 167     |

| * | Bt473 5 - 187     |

| * Bt4765 - 167  |

|-----------------|

| * Bt4785 - 167  |

| * Bt479 5 - 211 |

| * Bt492 5 - 237 |

| * Bt604         |

| * Bt605         |

| * Bt606         |

| * Bt687         |

| * Bt688         |

| * Bt689         |

| * Bt698         |

| * Bt7017-67     |

|                 |

\*New products

Brooktree Corporation 9950 Barnes Canyon Rd. San Diego, CA 92121 (619) 452-7580 (800) VIDEO IC TLX: 383 596 FAX: (619) 452-1249

# **Brooktree**®

# **Brooktree**®

|                             | Introduction                         |

|-----------------------------|--------------------------------------|

|                             | Quality Assurance                    |

|                             | Product Index                        |

| Imaging/Graphics            | VIDEODACs                            |

|                             | RAMDACs                              |

|                             | Peripherals                          |

|                             | <b>Imaging Products</b>              |

|                             | Application Notes                    |

| Automatic Test<br>Equipment | Timing/Comparators/<br>Drivers/Loads |

|                             | Data Conversion                      |

| Military                    | Military 883C Products               |

|                             | Packaging Information                |

|                             | Sales Offices                        |

ii

# **Brooktree**<sup>®</sup>

# PRODUCT DATABOOK 1989

Thank you for your interest in Brooktree products.

Our commitment is to provide a steady stream of innovative products that offer the highest quality, lowest cost/performance solutions and back them with comprehensive support services. These include timely and accurate technical information and responsive, experienced applications assistance.

At Brooktree, listening to customer's requirements is what we do first. Solving customer problems is what we do best.

Brooktree reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished by Brooktree Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Brooktree Corporation for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent or patent rights of Brooktree Corporation.

Copyright © 1989 Brooktree Corporation (all rights reserved)

VIDEODAC and RAMDAC are trademarks of Brooktree Corporation. Brooktree is a registered trademark of Brooktree Corporation. Personal System/2 and PS/2 are registered trademarks of IBM. Macintosh is a licensed trademark of Apple Computer, Inc.

This databook was published using ReadySetGo!, Cricket Draw, and Cricket Graph on a Macintosh II computer and LaserWriter II NTX. ReadySetGo! is a trademark of Manhattan Graphics, Inc.. LaserWriter is a trademark of Apple Computer, Inc. Cricket Draw and Cricket Graph are trademarks of Cricket Software, Inc.

# **Brooktree**®

**Imaging/Graphics**

Introduction

**Quality Assurance**

**Product Index**

**VIDEODACs**

**RAMDACs**

Peripherals

**Imaging Products**

**Application Notes**

Automatic Test Equipment Timing/Comparators/ Drivers/Loads

**Data Conversion**

Military

**Military 883C Products**

**Packaging Information**

**Sales Offices**

1

#### Company Facts

Brooktree began operations in 1983 following the development of an advanced architecture for data conversion. The architecture, invented by company co-founder and chief scientist Henry Katzenstein, permits the combination of high-performance analog and digital circuitry on a single monolithic integrated circuit which can be manufactured using standard bipolar or CMOS processes.

Brooktree Corporation is a privately held company located in San Diego, California. A 72,000 sq. ft. facility houses all design, test, and quality assurance activities as well as marketing, sales, and administration. Brooktree has established a worldwide network of distributors and factory representatives, with offices in the United States, Europe, and the Far East.

The company's products are manufactured under agreements with several domestic and international foundry sources. Second-source agreements are in effect with a number of suppliers.

Since its first volume shipments in 1985, Brooktree has achieved leadership share in the workstation graphics market, and a large share of the emerging market for PC graphics applications.

#### Products

Our first product, introduced in early 1985, was a 75 MHz 8-bit CMOS video digital-to-analog converter (VIDEODAC). By mid-1985, Brooktree had introduced six CMOS video digital-to-analog converter products (our VIDEODAC line) to the high-performance graphics market. Further system level integration led to our family of RAMDACs, which combine triple VIDEODACs, color palette RAMs, and pixel input multiplexers on a single chip. Recently introduced products include a 360 MHz bipolar RAMDAC and several next-generation CMOS RAMDACs.

In 1988, Brooktree entered the image acquisition market with it's first CMOS flash video A/D converter. Further system level integration led to our family of Image Digitizers, which combine one or more A/D converters and many additional functions required to digitize a video signal. Additional products are under development to enable image acquisition to be a "drop-in" solution.

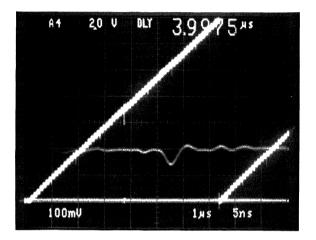

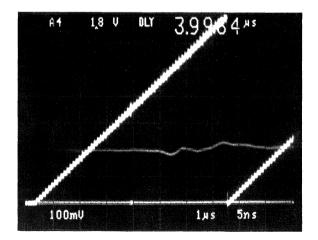

Products for the automatic test equipment and instrumentation markets include the industry's first octal 8-bit monolithic DAC and programmable timing verniers which achieve delay resolutions of as little as 20 picoseconds.

#### Strategy

Brooktree will combine the elements of its high-performance mixed signal design capabilities and proprietary test technology to provide a unique family of application-specific products. We will continue to develop highly-integrated products for use in computer graphics and imaging while introducing enabling technologies aimed at solving problems in the automatic test equipment and instrumentation markets.

## **Data Sheet Designations**

### **Advance Information**

This is the first official information released about a potential product. The datasheet contains basic information about the product and contains the target parametric and functional specifications. It usually precedes sample devices by approximately six months. This datasheet has the phrase "Advance Information" in the upper left corner on the front page.

### **Preliminary Information**

This datasheet is released with sample devices. It contains a more extensive discussion of device operation and provides more complete parametric information. The functional operation is fully defined and the parametric information is the result of early testing of the initial devices. Not all of the parametric specifications may be fully tested or characterized. This datasheet has the phrase "Preliminary Information" in the upper left corner on the front page.

#### **Final datasheet**

This datasheet evolves from the Preliminary Information datasheet. It is a result of test information collected from fully characterized devices. This datasheet is distinguished by the absence of any designation, except the part number, at the top of the front page.

## **Device Designations**

#### **Engineering Sample**

Devices which have exhibited most of the functionality for which it was designed. Engineering samples are used to enable selected customers to evaluate the device as early as possible.

While some of the AC and DC parameters may be tested, the accuracy or completeness of the testing is not guaranteed. In addition, the product has not been put through Brooktree's quality and reliability testing. They have standard marking with an additional "ES" marked on top of the package. These devices have a Preliminary datasheet under document control.

#### **Pre-Qual**

These devices have production silicon, testing, and burn-in. Most characterization is done, but the device must still pass a QA life-test qual. These devices have standard marking with an additional "PQ" marked on top of the package. These devices have a Preliminary datasheet under document control.

#### **Full Production**

These devices have production silicon, testing, burn-in, and have successfully passed a QA life-test qual. These devices have standard marking with no additional designators. These devices have a Final datasheet under document control.

# **Brooktree**®

**Imaging/Graphics**

Introduction

**Quality Assurance**

**Product Index**

**VIDEODACs**

**RAMDACs**

Peripherals

**Imaging Products**

**Application Notes**

Automatic Test Equipment Timing/Comparators/ Drivers/Loads

**Data Conversion**

Military

**Military 883C Products**

**Packaging Information**

**Sales Offices**

#### Introduction

The value of a product is measured by how well it is designed, manufactured and tested and how well it continues to perform over time. This value can be represented in quantitative terms by stating levels of quality and reliability. Brooktree determines these quality levels by performing industry recognized evaluation and monitoring programs for all products it manufactures.

Quality is a critical aspect of product success, and we have established an aggressive schedule of measuring, testing and monitoring the product to assure our customer that each device will perform to the highest quality and reliability standards. We have made substantial investments in experienced personnel and in state-of-the-art capital equipment for our design, manufacturing and quality assurance departments.

#### **Product** Quality

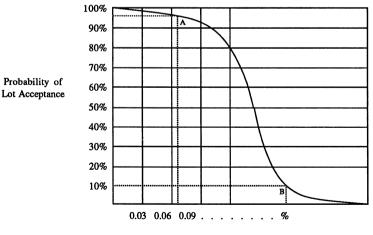

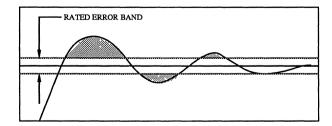

Quality is a measure of product conformance to the specifications. This is determined by measuring the percentage of defects in a given sample size. The Quality Assurance program includes material inspections which employ industry-standard Lot Tolerance Percent Defective (LTPD) and Acceptable Quality Level (AQL) sampling plans. These sampling procedures assure with a high degree of confidence that a lot will not be approved for shipment if certain levels of quality are not met. For sampling plans, the operating characteristic curve illustrated in Figure 1 shows the relationship of lot quality versus probability of acceptance. Point A on the curve is termed AQL; it signifies the lot quality in percent defective (0.065%) that will give a high probability (95%) of lot acceptance. Point B on the curve is termed LTPD and signifies the unsatisfactory level of quality where the lot will be rejected 90% of the time. Brooktree performs quality conformance testing using an acceptance sampling method based on MIL-STD-105D and MIL-M-38510H.

Manufacturing process control is accomplished through the efforts of the Document Control Department. An effective plan for document sign-off and distribution ensures that updated documents are reviewed and are made available immediately to affected operations.

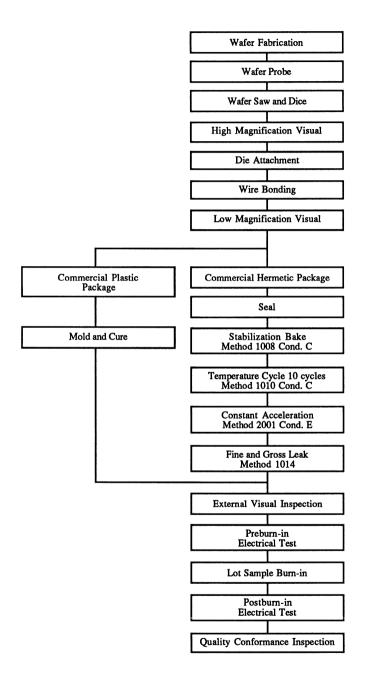

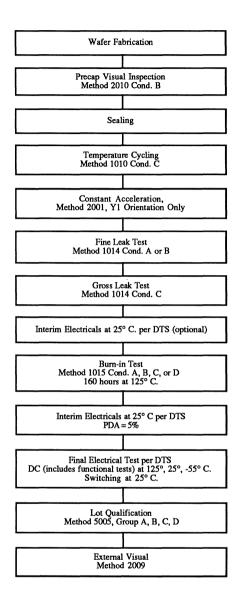

Brooktree's Quality Assurance program imposes strict requirements on vendors, and monitors their performance through inspection of incoming materials and regular audits of the vendor's facilities and quality methods. Figure 2 is a generalized standard product manufacturing flow which illustrates the manufacturing steps and quality assurance

Lot Quality (Percent Defective)

Figure 1. Lot Quality vs. Probability of Acceptance.

Figure 2. Standard Product Manufacturing Flow.

monitors used for all our products. The Brooktree quality assurance program conforms to the program guidelines as specified in MIL-Q-9858.

#### **Product** Reliability

Reliability is quality over time, a measurement of how long the product continues to perform to original specifications. This must be guaranteed by using a worst-case design methodology, precisely controlled wafer-processing, and manufacturing assembly and testing to highest quality standards.

Verification of product reliability is accomplished through accelerated life testing and physical and environmental stress testing. The stress tests performed for product qualification are listed in Tables 1 and 2. These tests are repeated at six-month intervals to verify continuing process and product integrity. Strict engineering change control procedures are used to assure a controlled process.

Screening is performed to eliminate early-failure devices and to conform to military requirements. Military grade products are tested in conformance to MIL-STD-883C; refer to the Military Section of this manual for further details. The basic method used to estimate product life is accelerated environmental testing. These tests expose the product to stresses greater than expected in actual use. The number of device failures that occur can be related to the magnitude of the stress applied. The common practice is to express the results in failures in 10<sup>9</sup> hours, or FITs (one FIT is equal to one failure per billion device hours of operation. It can also be expressed in the common notation of 0.0001% failures per 1000 hours).

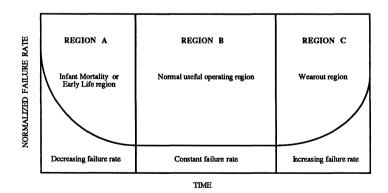

Figure 3 is an idealized graph of device failure rate vs time, often called the Bathtub Curve. Three distinct regions are of importance. Region A is characterized by high failure rates that show up in early usage and then decrease with time. This area of early life failures needs to be eliminated prior to product being shipped to the final consumer. The early life failure rate is minimized by screening procedures, the most common of which is burn-in testing performed at the device and/or system level. Region B is characterized by a constant failure rate, and indicates the normal operating region that will assure maximum useful service and reliability. Region C indicates the wearout region where device failure rate increases. The wearout region is seldom reached in well-designed semiconductor integrated circuits under normal operating conditions. Results of accelerated life testing are extrapolated to estimates of in-service reliability through use of the Arrhenius model.

#### **Product** Development

Quality and Reliability planning begins with the product development cycle. It is vital that every possible effort to increase the reliability is made during the development cycle. This is achieved by defining specific design goals, using proven reliable materials and manufacturing methods, and implementing controlled production processes with accurate testing and monitoring.

Figure 3. Device Failure Rate vs. Time.

#### Design

Brooktree's engineering department has established a comprehensive design methodology developed to produce reliable devices. Product definition begins with experienced system designers who can accurately specify the electrical interface and functional boundary requirements. This assures that all new devices will have specifications and worst case operating and environmental conditions identified before design begins.

Design engineers use schematic capture and simulation software to verify the operation of the design over temperature, power supply and processing variations. Design reviews require designers to demonstrate to the Quality Assurance department that their design will meet or exceed reliability rules, including allowable amount of electrostatic discharge (ESD), latch-up protection (CMOS products), and current density (to prevent metal migration). Computer simulation of each circuit design is done using a worst case methodology.

Conformance to strict layout rules gives products immunity to process variation while maximizing reliability. An extensive set of checks is provided by several state-of-the-art CAD tools that assure the design layout is correct and that wafers can be consistently processed with confidence in yield and reliability.

#### Wafer Probe

Wafer probe is performed at Brooktree to ensure the tightest quality and reliability controls early in the life of the product. Wafer probe test conditions and limits are guard banded to ensure early removal of defective devices. Correlation between the final test programs and probe programs is an effective gate to prevent a non-functional device from entering the assembly operation. Rejected dice are marked with an ink dot to allow easy identification after the individual die is scribed from the wafer.

#### Device Assembly

The Quality Assurance department monitors the performance of various processing steps by requiring mandatory sampling of each lot moving through critical quality operations. We have instituted eight sampling points or gates in the assembly area: wafer inspection, material inspection, 1st QA die visual (high magnification), die attach control, 2nd QA die visual (low magnification), QA hermeticity check, QA final inspection and QA outgoing audit. Daily monitoring and audits of equipment and operators ensure that the final product meets all predefined quality criteria.

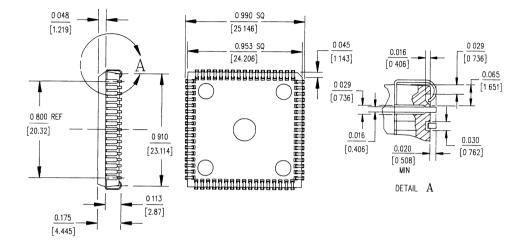

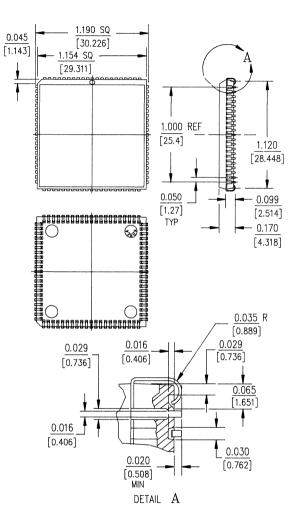

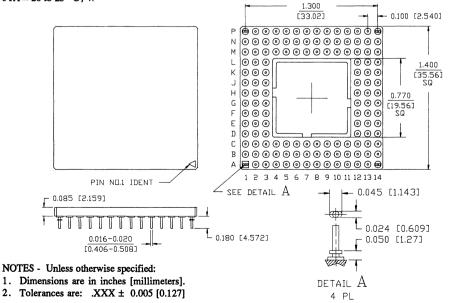

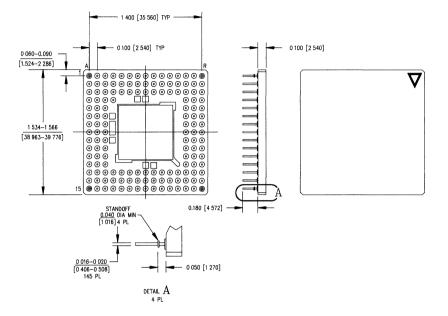

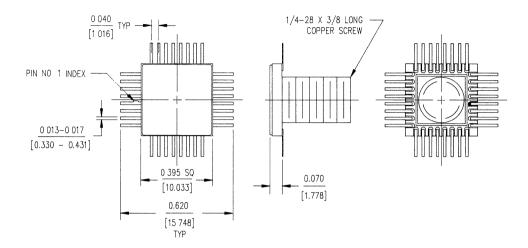

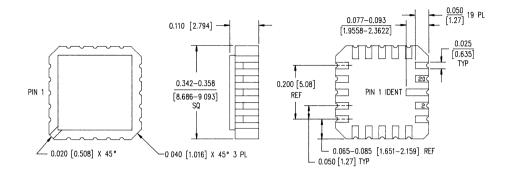

#### Device Packaging

Brooktree packaging uses standard, semi-custom and custom packages. Package outlines and foot prints comply with JEDEC and SEMI standards whenever possible. Since product performance is affected by packaging design, custom packages are constructed when necessary to preserve the reliability and performance of the enclosed device.

#### Final Testing

Final electrical testing is performed at Brooktree using state-of-the-art test equipment and techniques. Test parameters and test conditions are such that proper performance is guaranteed to data sheet requirements. Test limits are guard banded to compensate for tester inaccuracy, thereby minimizing measurement correlation errors between the factory and customer. To comply with quality conformance requirements, QA verifies proper processing, proper electrical performance over specified operating temperatures and voltage ranges, and visual criteria.

#### Qualification

All products we manufacture are labeled to show the classification of the products reliability for consumer use. Each product datasheet contains a designation as to the product development and specification parameters status. The product datasheet designations are Advanced, Preliminary and Final. When the device has been fully characterized to all the specifications and datasheet parameters, and has completed the environmental tests outlined in Tables 1 and 2, it is labeled production worthy and labeled a Final Data Sheet.

#### Failure Analysis

Even under the strictest of standards, failures do occur. To control this situation and learn from it, the failure analysis group identifies reliability problems and performs corrective action on failures from in-house stress testing as well as customer field returns. Brooktree provides customers with specific feedback so that the customer can be assured that appropriate action has been taken.

2 - 5

| Description                                                                                                                             | Methods and Conditions*                                                                                                        | Sample /<br>Max. Reject   | Notes                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------|

| High Temperature<br>Operating Life<br>Electrical                                                                                        | 2000 hours, TA = 125° C. ***<br>TA = Tmax                                                                                      | 280<br>(<400 FIT)<br>**** | electrical at 16, 48, 168,<br>500, 1000, 1500, 2000<br>hours   |

| High Temperature<br>Storage<br>Electrical                                                                                               | 2000 hours, TA = 200° C. $TA = Tmax$                                                                                           | 55 / 0                    | electrical at 500,<br>1000, 1500, 2000<br>hours                |

| Temperature Cycle<br>Electrical                                                                                                         | Method 1010, condition C,<br>-65° C. / +150° C., 500 cycles<br>TA = Tmax                                                       | 116 / 0                   |                                                                |

| Thermal Shock<br>Electrical                                                                                                             | Method 1011, condition B,<br>-55° C. / +125° C., 200 cycles<br>TA = Tmax                                                       | 116 / 0                   | electrical every 500<br>cycles                                 |

| Pre-conditioning<br>Temperature Cycle<br>Temperature Cycle<br>Electrical                                                                | -40° C. / +150° C., 20 cycles<br>0° C. / +125° C. 3000 cycles<br>TA = Tmax                                                     | 153 / 0                   |                                                                |

| Pre-conditioning<br>Temperature Cycle<br>Pre-conditioning<br>Temperature/Humidity<br>Steady-State<br>Temperature/Humidity<br>Electrical | -65° C. / +150° C., 10 cycles<br>85° C. / 85% RH, 24 hours,<br>unbiased<br>85° C. / 85% RH, 1500 hours,<br>biased<br>TA = Tmax | 195 / 1                   | plastic package only<br>electrical at 500, 1000,<br>1500 hours |

| Pressure Cooker<br>Electrical                                                                                                           | 125° C., 2.3 atm, 288 hours<br>TA = Tmax                                                                                       | 77 / 1                    | plastic package only                                           |

| Destructive Physical<br>Analysis                                                                                                        | SEM - surface and cross<br>section                                                                                             | 3 sets                    | 1 set from each of 3<br>wafer lots                             |

\*Test methods reference MIL-STD-883C.

\*\*\*\*FIT shall be calculated using the Ahhrenius acceleration model and the following assumptions:

Ea = 0.5 eV if no failures; if failures, Ea to be determined based upon failure mechanism.

Ts = 55° C. (derating temperature)

confidence level = 60%

#### Table 1. Wafer Foundry Tests\*\*.

<sup>\*\*</sup>Samples to be selected from 3 wafer lots (each lot shall be processed with a minimum of 1 week separating it and the other two wafer lots.

<sup>\*\*\*</sup>Power supplies shall be set to 0.5v less than the absolute maximum specified supply voltage; TA shall be reduced, if necessary, to guarantee TJ to be less than 175° C. for ceramic packages, or less than 150° C. for plastic packages.

| Description                                                                                     | Methods and Conditions*                                                                                                                                                     | Sample /<br>Max. Reject      | Notes                                 |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------|

| External Lead Plating<br>Thickness<br>Solderability                                             | Method 2003                                                                                                                                                                 | 4/0<br>4 units/<br>all leads |                                       |

| Resistance to Solvents                                                                          | Method 2015                                                                                                                                                                 | 4/0                          |                                       |

| Internal Visual<br>Bond Strength<br>Die Shear                                                   | Method 2010<br>Method 2011<br>Method 2019                                                                                                                                   | 4/0                          |                                       |

| External Lead<br>Integrity<br>Fine Leak<br>Gross Leak                                           | Method 2004, condition B<br>Method 1014, condition A or B<br>Method 1014, condition C                                                                                       | 34 / 2                       | for CERDIP only<br>for CERDIP only    |

| Temperature Cycle<br>Electrical                                                                 | Method 1010, condition C,<br>-65° C. / +150° C., 500 cycles<br>TA = Tmax                                                                                                    | 116 / 0                      |                                       |

| Thermal Shock<br>Electrical                                                                     | Method 1011, condition B,<br>-55° C. / +125° C., 200 cycles<br>TA = Tmax                                                                                                    | 116 / 0                      |                                       |

| Preconditioning<br>Temperature Cycle<br>Temperature Cycle<br>Electrical                         | -40° C. / +150° C., 20 cycles<br>0° C. / +125° C., 3000 cycles<br>TA = Tmax                                                                                                 | 153 / 0                      | electrical every 500<br>cycles        |

| Steady-State Temp.<br>and Humidity<br>Visual                                                    | 85° C. / 85% RH,<br>1500 hours, biased                                                                                                                                      | 50 / 0                       | empty (dummy) packages<br>may be used |

| Mechanical Shock<br>Vibration<br>Constant Acceleration<br>Fine Leak<br>Gross Leak<br>Electrical | Method 2002, condition B<br>Method 2007, condition A<br>Method 2001, condition E,<br>Y1 axis only<br>Method 1014, condition A or B<br>Method 1014, condition C<br>TA = Tmax | 34 / 2                       |                                       |

### Table 2. Monolithic Hermetic Package Assembly Tests\*\*.

| Description                                                              | Methods and Conditions*                                                                                                                          | Sample /<br>Max. Reject | Notes                                 |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------|

| Salt Atmosphere<br>Fine Leak<br>Gross Leak                               | Method 1009<br>Method 1014, condition A or B<br>Method 1014, condition C                                                                         | 34 / 2                  |                                       |

| Resistance to<br>Soldering Heat<br>Fine Leak<br>Gross Leak<br>Electrical | <ul> <li>15 sec dip to with 1/8" of body<br/>in solder at 260° C.</li> <li>Method 1014, condition A or B<br/>Method 1014, condition C</li> </ul> | 22 / 0                  |                                       |

| Destructive Physical<br>Analysis                                         | SEM - surface and<br>cross-section                                                                                                               | 3 sets                  | 1 set from each of 3<br>assembly lots |

\*Test methods reference MIL-STD-883C.

\*\*Samples to be selected from 3 assembly lots (each lot shall be processed with a minimum of 1 week separating it and the other two assembly lots.

# Table 2. Monolithic Hermetic Package Assembly Tests\*\*. (Continued)

| Description                                                                                                                           | Methods and Conditions*                                                                                                       | Sample /<br>Max. Reject       | Notes                                      |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------|

| External Lead Plating<br>Thickness<br>Solderability                                                                                   | Method 2003                                                                                                                   | 4 / 0<br>4 units /<br>2 leads |                                            |

| Resistance to Solvents                                                                                                                | Method 2015                                                                                                                   | 4/0                           |                                            |

| X-Ray                                                                                                                                 |                                                                                                                               | 4/0                           |                                            |

| Mechanical Shock<br>Electrical                                                                                                        | Method 2002, condition B<br>TA = Tmax                                                                                         | 25 / 1                        |                                            |

| Temperature Cycle<br>Electrical                                                                                                       | Method 1010, condition C,<br>-65° C. / +150° C., 500 cycles<br>TA = Tmax                                                      | 116 / 0                       |                                            |

| Thermal Shock<br>Electrical                                                                                                           | Method 1011, condition B,<br>-55° C. / +125° C., 200 cycles<br>TA = Tmax                                                      | 116 / 0                       |                                            |

| Preconditioning<br>Temperature Cycle<br>Temperature Cycle<br>Electrical                                                               | -40° C. / +150° C., 20 cycles<br>0° C. / +125° C., 3000 cycles<br>TA = Tmax                                                   | 153 / 0                       | electrical every 500<br>cycles             |

| Preconditioning<br>Temperature cycle<br>Preconditioning<br>Temperature/Humidity<br>Steady-State<br>Temperature/Humidity<br>Electrical | -65° C. / +150° C. 10 cycles<br>85° C. / 85% RH, 24 hours,<br>unbiased<br>85° C. / 85% RH, 1500 hours,<br>biased<br>TA = Tmax | 195 / 1                       | electrical at 500, 1000,<br>and 1500 hours |

| Pressure Cooker<br>Electrical                                                                                                         | 125° C., 2.3 atm, 288 hours<br>TA = Tmax                                                                                      | 77 / 1                        |                                            |

## **Quality Assurance**

| Description                                                                                                                                     | Methods and Conditions*                                                                                                                          | Sample /<br>Max. Reject   | Notes                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------|

| Salt Atmosphere                                                                                                                                 | Method 1009                                                                                                                                      | 34 / 2                    |                                        |

| High Temperature<br>Operating Life<br>Electrical                                                                                                | TA = 125° C. (TJ < 150° C.),<br>1500 hours<br>TA = Tmax                                                                                          | 150<br>(< 400 FIT)<br>*** | electrical at 500, 1000,<br>1500 hours |

| Preconditioning<br>Pressure Cooker<br>Infra-Red Reflow (IR)<br>Pressure Cooker<br>Electrical                                                    | 125° C., 2.3 atm, 72 hours<br>3 cycles<br>125° C., 2.3 atm, 200 hours<br>TA = Tmax                                                               | 45 / 0                    | PLCC packages only                     |

| Preconditioning<br>Pressure Cooker<br>Infra-Red Reflow (IR)<br>Temperature Cycle<br>Electrical                                                  | 125° C., 2.3 atm, 72 hours<br>3 cycles<br>Method 1010, condition C<br>-65° C. / +150° C., 500 cycles<br>TA = Tmax                                | 45 / 0                    | PLCC packages only                     |

| Preconditioning<br>Temperature Cycle<br>Preconditioning<br>Temperature/Humidity<br>Vapor Phase Solder<br>Pressure Cooker<br>Electrical / Visual | Method 1010, condition C,<br>-65° C. / +150° C., 20 cycles<br>85° C. / 85% RH, 72 hours,<br>unbiased<br>125° C., 2.3 atm, 200 hours<br>TA = Tmax | 45 / 0                    | PLCC packages only                     |

| Resistance to<br>Soldering Heat<br>Electrical                                                                                                   | 15 sec dip to within 1/8" of body<br>in solder at 260 °C.<br>TA = 25 °C.                                                                         | 22 / 0                    |                                        |

| Destructive Physical<br>Analysis                                                                                                                | SEM - surface and cross-section                                                                                                                  | 3 sets                    | 1 set from each of 3<br>assembly lots  |

\*Test methods reference MIL-STD-883C.

Ea = 0.5 eV if no failures; if failures, Ea to be determined based upon failure mechanism.

Ts = 55° C. (derating temperature)

confidence level = 60%

# Table 3.Monolithic Plastic Package Assembly Tests\*\*.(Continued)

<sup>\*\*</sup>Samples to be selected from 3 wafer lots (each lot shall be processed with a minimum of 1 week separating it and the other two wafer lots.

<sup>\*\*\*</sup>FIT shall be calculated using the Ahhrenius acceleration model and the following assumptions:

### **Terms and Definitions**

#### Activation Energy

The excess energy over the ground state which must be acquired by an atomic or molecular system in order for a specific process to occur. In semiconductor materials this energy is usually equal to 0.96 eV.

#### Arrhenius Model (Acceleration Factor)

The Arrhenius Model defines a relationship between the failure rate and time that is commonly used in correlating accelerated life environmental testing to useful lifetime. The equation is used to calculate failure rates based on lower junction temperatures and normal operating environmental conditions.

The acceleration factor is the reaction rate of a process at one temperature compared with the reaction rate of the same process at another temperature. The acceleration factor equation determines the multiplication factor of time that the change in temperature caused on the reaction process.

$$AF = e [E/K (1/T_1 - 1/T_2)]$$

Where:

AF = Acceleration Factor

- e = natural logarithm base of 2.71828

- E = the activation energy for semiconductor material

K = Boltzmann's Constant

(8.61 x 10<sup>-5</sup> eV / Kelvin )

T<sub>1</sub> = Lower temperature in Degrees Kelvin

$T_2$  = Higher temperature in Degrees Kelvin

Example: The AF for a temperature change from  $85^{\circ}$  C. to  $125^{\circ}$  C. is 393.8. This factor is the time multiplication factor: 1 hour at  $125^{\circ}$  C. is equivalent to 393.8 hours (over 16 days) at  $85^{\circ}$  C.

#### Bias

The electrical connection to the device pins that allows specified signals, loading, and power supply voltage to be applied. Often referred to as "electrical bias."

#### Biased Humidity

An environmental test where the subject device is exposed to high humidity and temperature conditions (85% relative humidity and 85° C.) while having the device under an electrical bias. This procedure is designed to measure the device's susceptibility to electrolysis or electrolytic corrosion. The acceleration factor for a humidity change from 50% to 85% has been standardized as approximately 10. In analyzing bias humidity and temperature are estimated separately.

#### Burn-In

A thermal and electrical stress test designed to eliminate early failures. The early device failures (infant mortality) are detected and removed, thus enhancing reliability.

#### Environmental Tests

Several tests that determine the long-term stability and reliability of products. The product is exposed to various conditions and extremes of temperature, humidity, pressure or mechanical stress that stimulates potential faults to appear, and accelerate detection of device failures.

#### Failure in Time (FIT)

A standard reliability unit that measures the device failure rate as a function of device hours. One FIT is equal to one device failure per billion device hours of operation (1 FIT = 0.0001% failures / 1000 hours).

#### Infant Mortality

Initial failures of devices that occur in early life operation. This is the region of the device failure rate curve where the device failure rate decreases with time. Product reliability is enhanced when environmental screening eliminates these early failures region.

### Terms and Definitions (continued)

#### Pressure Cooker

A test that subjects the device to an atmosphere of high temperature moisture under a pressure of approximately two atmospheres. This test exposes susceptibility to galvanic corrosion due to chemical instability of the encapsulating materials.

#### Qualification

The test procedures as defined by the Quality Assurance Department that a product must survive before being considered a reliable manufacturing product.

#### Quality\*

The extent to which a product successfully serves the purpose of the user, during usage, is called "fitness for use." This concept of fitness for use is popularly called quality. Several parameters can be used to characterize product quality. Quality of design is a technical measure of the level or degree of excellence of the product to meet it's intended needs of the user. Three activities that compose the quality of design are; Quality of market research, Quality of concept, and Quality of specification. Quality of conformance is the extent to which the product conforms to the design, and can be measured by testing to the product specification. Conformance also is termed Quality of manufacturing or Quality of production. The quality of products over time is characterized by the time-oriented factors such as; availability, reliability, and maintainability.

#### Quality Assurance (QA)

The activity of providing, to all concerned, the evidence needed to establish confidence and assurance that all the activities which affect product quality are being performed adequately.

#### Reliability

Quality of products over time can be stated by the products ability to perform without failure. The classic definition is "the probability of a product performing without failure a specified function under given conditions for a specified period of time."

#### **Reliability** Growth

The continuing efforts to reduce failure rates result in continued improvements (or growth) in reliability. This takes place in the design and manufacturing phases, and when additional product improvements are needed as determined from field performance data.

#### Sampling

Inspection method to determine lot quality by careful examination of a small number of devices from the lot. A sampling plan is used to set the sample size, based on the desired quality level.

#### Screening

The process of subjecting all products to non-destructive stresses to accelerate and identify early failures.

#### Stress

An extreme environmental, electrical or physical condition applied to a device to evaluate the device performance or to accelerate reaction rates.

#### Temperature Cycling

A test that determines the thermal expansion compatibility of materials used in device packaging. The test exposes the device to temperature extremes, typically a low temperature of  $-65^{\circ}$  C. to a high temperature of  $+150^{\circ}$  C. The device is under no electrical bias.

#### Thermal Shock

This is a temperature cycling test in which the temperature transitions are very rapid, less than 10 seconds. The device is immersed in suitable liquid baths, each having extreme high and low temperatures to expose failures such as device cracking, and package leaking.

\*QUALITY CONTROL HANDBOOK, Third Edition McGraw Hill 1974, JURAN, Joseph M., Frank M. Gryna Jr., and R.S. Bingham Jr.

# **Brooktree**<sup>®</sup>

**Imaging/Graphics**

Introduction

**Quality Assurance**

**Product Index**

VIDEODACs

**RAMDACs**

Peripherals

**Imaging Products**

**Application Notes**

Automatic Test Equipment Timing/Comparators/ Drivers/Loads

**Data Conversion**

Military

**Military 883C Products**

**Packaging Information**

**Sales Offices**

## **Product Index**

| Bt101     | 50, 30 MHz Triple 8-bit VIDEODAC 4 - 5                                             |

|-----------|------------------------------------------------------------------------------------|

| Bt101/883 | 30 MHz MIL-STD-883 Version of Bt101 11 - 15                                        |

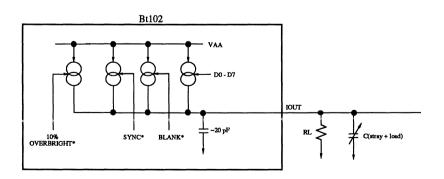

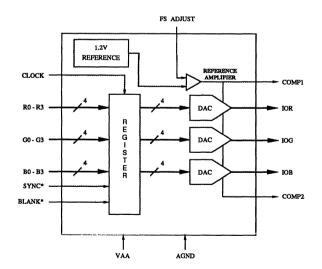

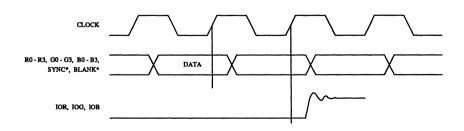

| Bt102     | 75 MHz Single 8-bit VIDEODAC with Programmable Setup 4 - 19                        |

| Bt102/883 | 50 MHz MIL-STD-883 Version of Bt102 11 - 27                                        |

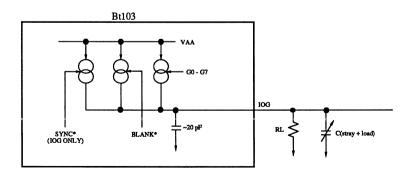

| Bt103     | 75, 30 MHz Triple 4-bit VIDEODAC 4 - 33                                            |

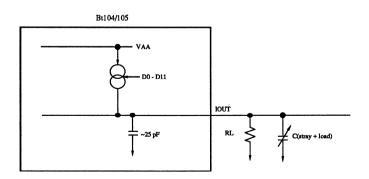

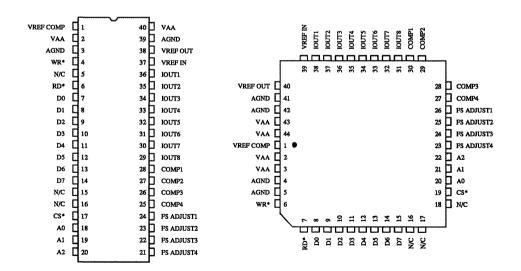

| Bt104     | 40 ns Single 12-bit D/A Converter, Unlatched Data Inputs 10 - 5                    |

| Bt105     | 40 ns Single 12-bit D/A Converter, Latched Data Inputs 10 - 5                      |

| Bt106     | 50, 30 MHz Single 8-bit VIDEODAC 4 - 47                                            |

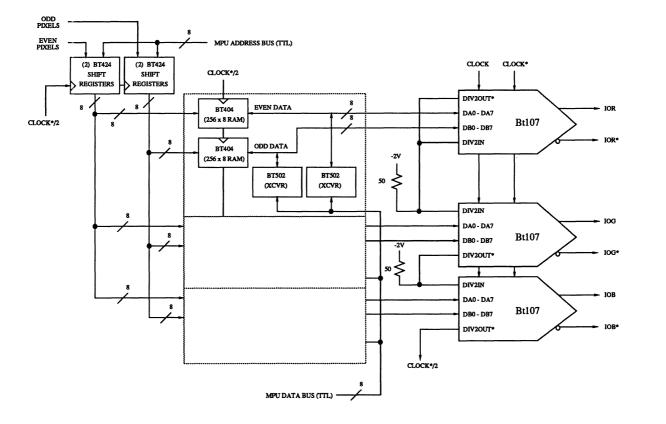

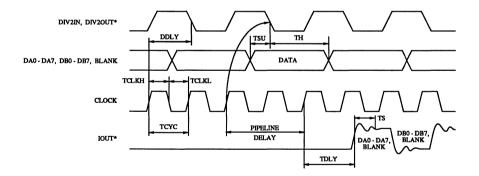

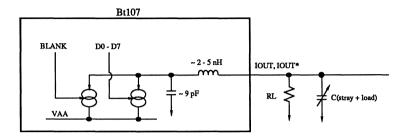

| Bt107     | 400 MHz Single 8-bit VIDEODAC with 2:1 Multiplexed Pixel Inputs<br>(10KH/100K ECL) |

| Bt109     | 250 MHz Triple 8-bit VIDEODAC, TDC1318 Pin Compatible(10KH ECL)                    |

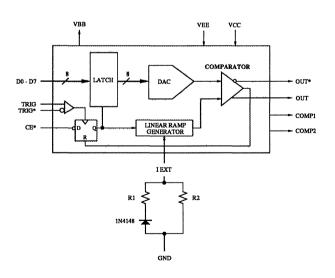

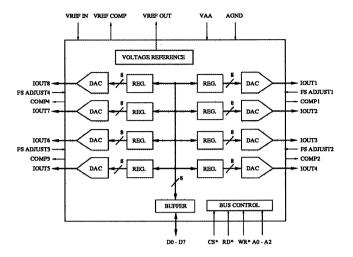

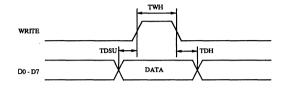

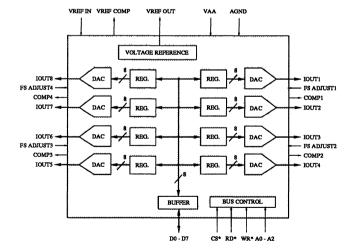

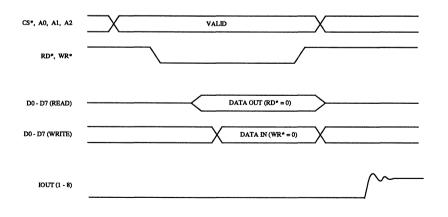

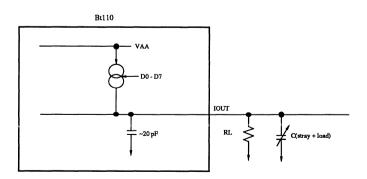

| Bt110     | 100 ns Octal 8-bit D/A Converter with Standard MPU Interface 10 - 17               |

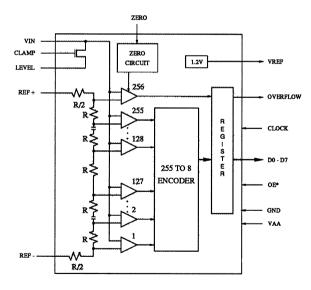

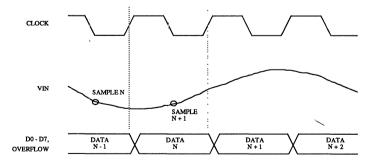

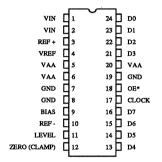

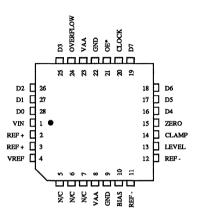

| Bt208     | 18 MSPS 8-Bit Flash Video A/D Converter                                            |

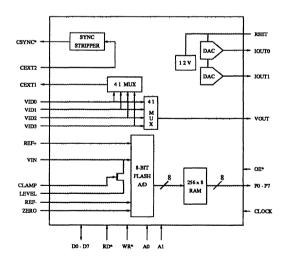

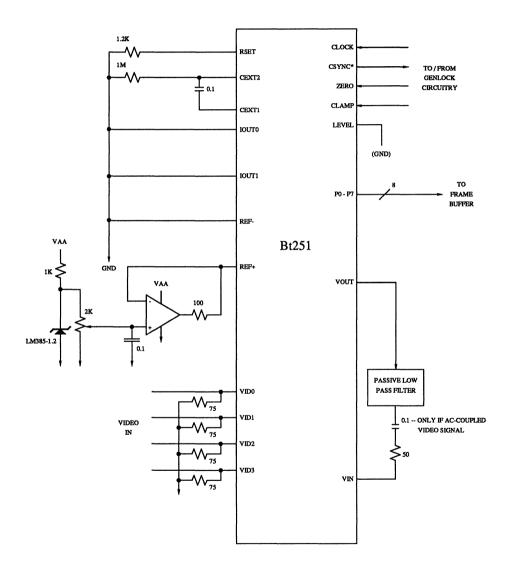

| Bt251     | 15 MSPS Single Channel Image Digitizer                                             |

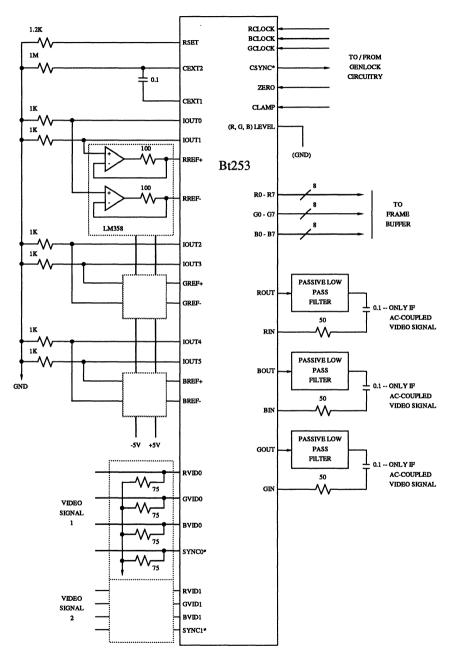

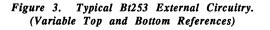

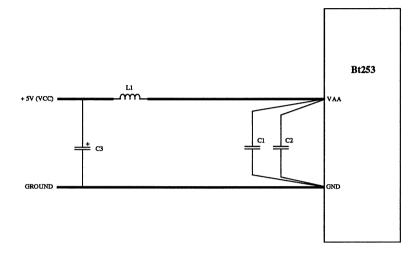

| Bt253     | 15 MSPS Triple Channel Image Digitizer                                             |

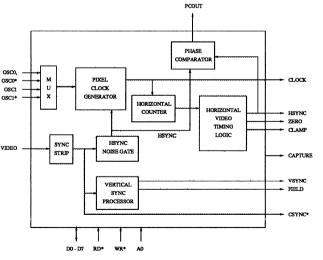

| Bt261     | HSYNC Genlock Controller                                                           |

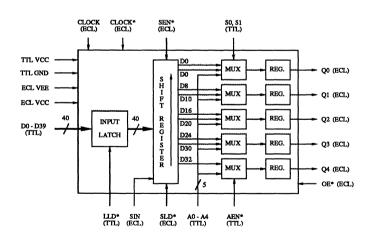

| Bt424     | 250 MHz 40-bit Multi-Tap Video Shift Register (10KH ECL/TTL) 6 - 5                 |

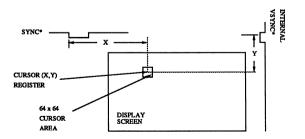

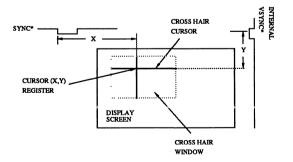

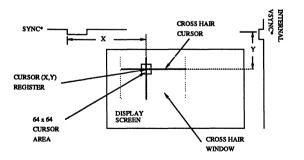

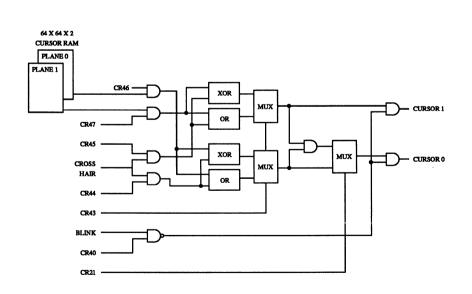

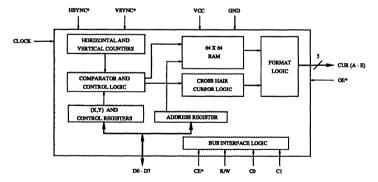

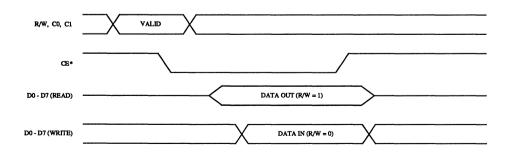

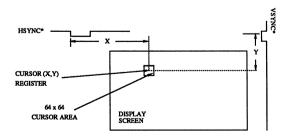

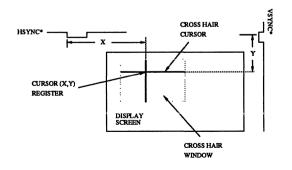

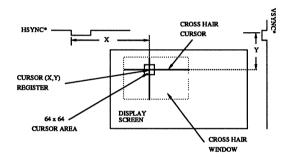

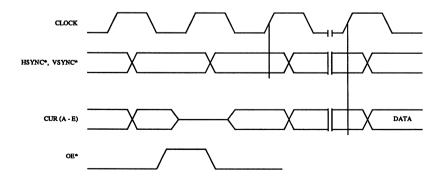

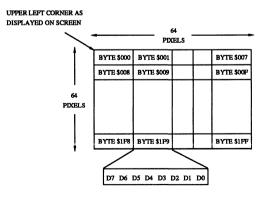

| Bt431     | 64 x 64 Pixel User-Definable Cursor, Cross Hair Cursor                             |

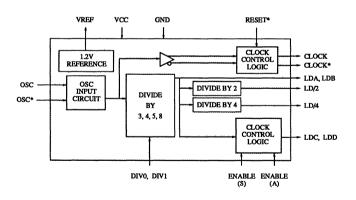

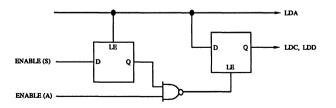

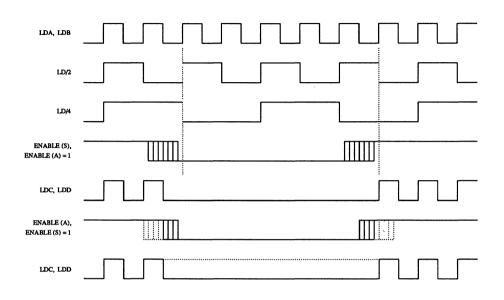

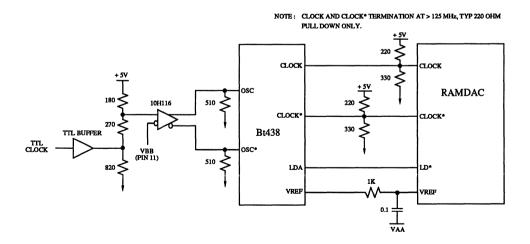

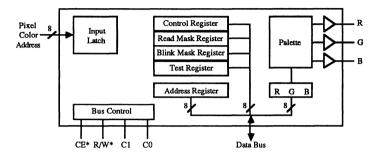

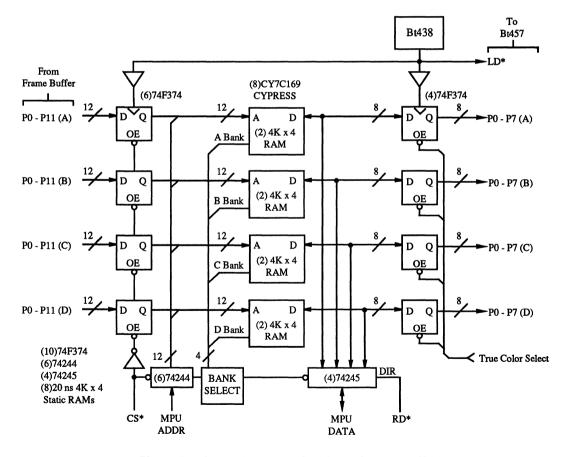

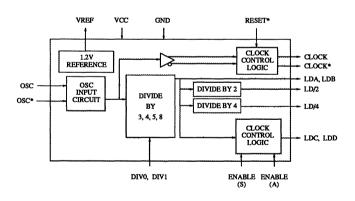

| Bt438     | 250 MHz Clock Generator Chip for CMOS RAMDACs                                      |

| Bt438/883 | 250 MHz MIL-STD-883 Version of Bt438 11 - 41                                       |

| Bt439     | 200 MHz Clock Generator/Synchronizer Chip for CMOS RAMDACs 6 - 49                  |

# **Product Index (continued)**

| Bt450     | 70, 50, 30 MHz Triple 4-bit RAMDAC with 16 x 12 RAM 5 - 5                                                            |

|-----------|----------------------------------------------------------------------------------------------------------------------|

| Bt451     | 125, 110, 80 MHz Triple 4-bit RAMDAC with 256 x 12 RAM,         4:1 or 5:1 Multiplexed Pixel Inputs                  |

| Bt453     | 66, 40 MHz Triple 8-bit RAMDAC with 256 x 24 RAM 5 - 51                                                              |

| Bt453/883 | 40 MHz MIL-STD-883 Version of Bt453 11 - 43                                                                          |

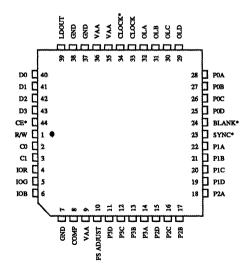

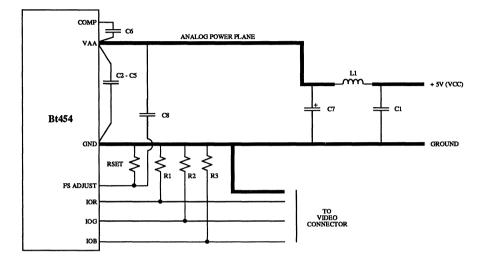

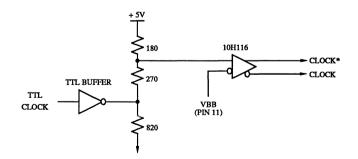

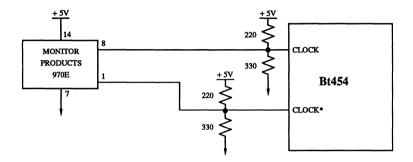

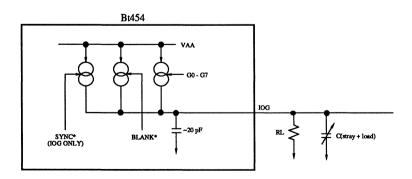

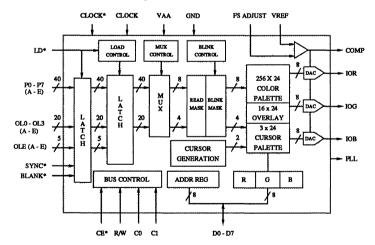

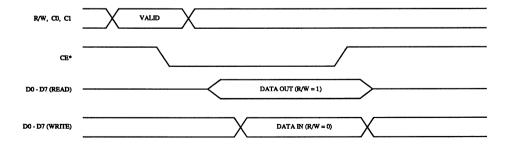

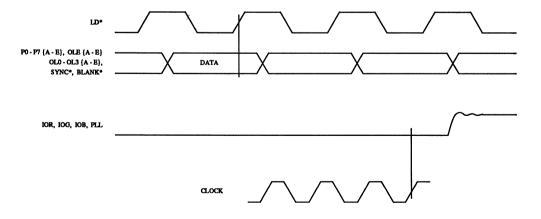

| Bt454     | 170, 110 MHz Triple 4-bit RAMDAC with 16 x 12 RAM,4:1 Multiplexed Pixel Inputs.5 - 67                                |

| Bt457     | 125, 110, 80 MHz Single 8-bit RAMDAC with 256 x 8 RAM,         4:1 or 5:1 Multiplexed Pixel Inputs                   |

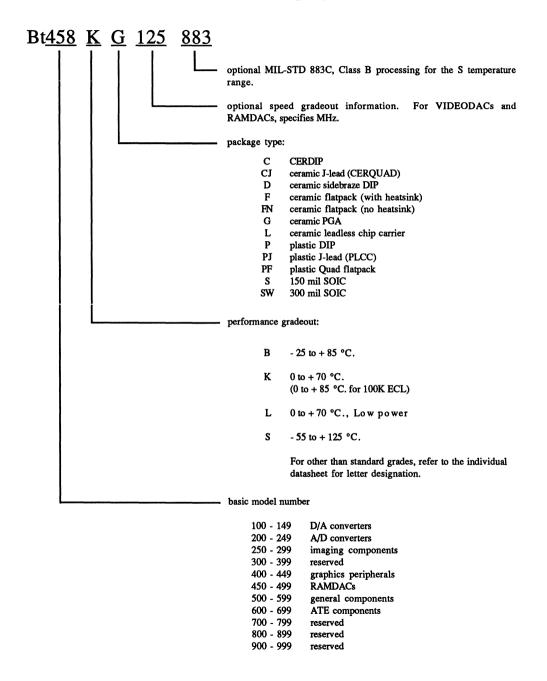

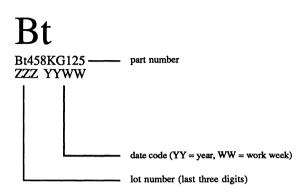

| Bt458     | 170, 125, 110, 80 MHz Triple 8-bit RAMDAC with 256 x 24 RAM,<br>4:1 or 5:1 Multiplexed Pixel Inputs                  |

| Bt458/883 | 110 MHz MIL-STD-883 Version of Bt458 11 - 57                                                                         |

| Bt459     | 135, 110, MHz Triple 8-bit RAMDAC with 256 x 24 RAM,<br>1:1, 4:1, or 5:1 Multiplexed Pixel Inputs, 64 x 64 Cursor    |

| Bt460     | 135, 110, 80 MHz Triple 8-bit RAMDAC with 512 x 24 RAM,<br>3:1, 4:1, or 5:1 Multiplexed Pixel Inputs, On-Chip Cursor |

| Bt461     | 170, 135, 110, 80 MHz Single 8-bit RAMDAC with 1024 x 8 RAM,<br>3:1, 4:1, or 5:1 Multiplexed Pixel Inputs            |

| Bt468     | 225, 200, 170 MHz Triple 8-bit RAMDAC with 256 x 24 RAM,<br>8:1 Multiplexed Pixel Inputs, 64 x 64 Cursor             |

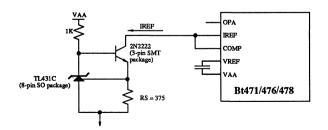

| Bt471     | 80, 66, 50, 35 MHz Triple 6-bit RAMDAC with 256 x 18 RAM 5 - 167                                                     |

| Bt473     | 80, 66, 50, 35 MHz Triple 8-bit True-Color RAMDAC with (3)<br>256 x 8 RAMs                                           |

| Bt476     | 80, 66, 50, 35 MHz Triple 6-bit RAMDAC with 256 x 18 RAM 5 - 167                                                     |

| Bt478     | 80, 66, 50, 35 MHz Triple 8-bit RAMDAC with 256 x 24 RAM 5 - 167                                                     |

| Bt479     | 80, 66, 50, 35 MHz Triple 8-bit RAMDAC with 1024 x 24 RAM,<br>Window Management                                      |

| Bt492     | 360 MHz Single 8-bit RAMDAC with 256 x 8 RAM                                                                         |

# **Product Index (continued)**

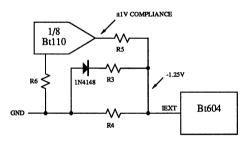

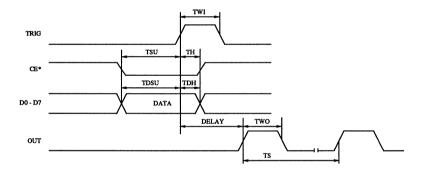

| Bt604 | Dynamically Programmed Timing Edge Vernier, 15 ps Resolution 9 - 5  |

|-------|---------------------------------------------------------------------|

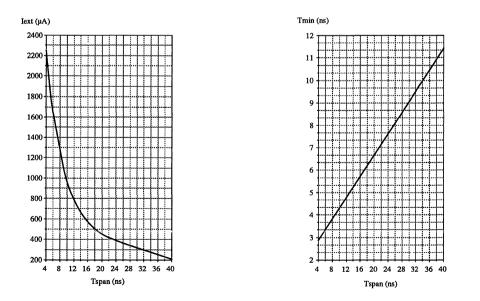

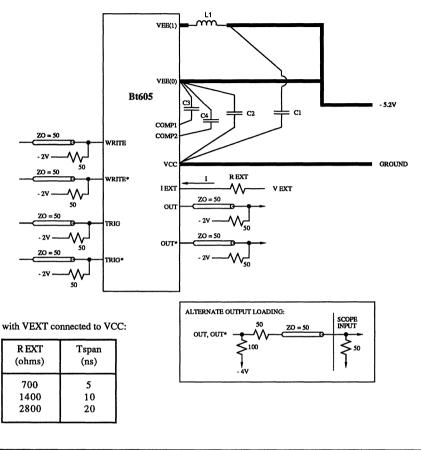

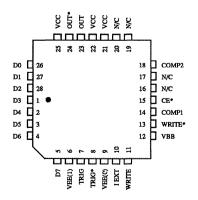

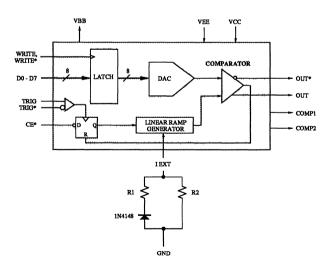

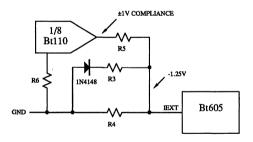

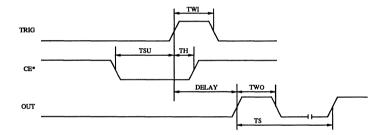

| Bt605 | Programmable Timing Edge Vernier, 15 ps Resolution                  |

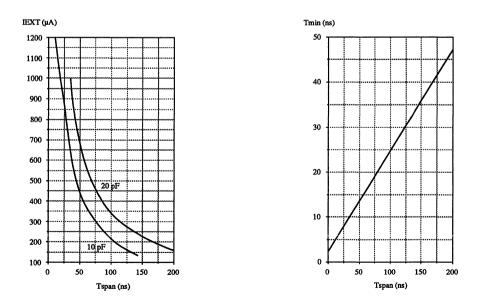

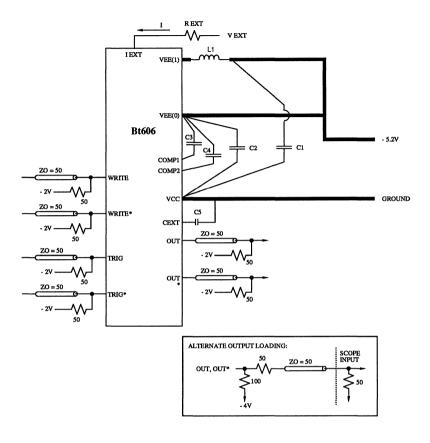

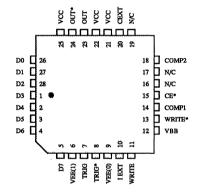

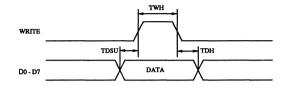

| Bt606 | Programmable Timing Edge Delay, 20 ns to 200 ns Span                |

| Bt687 | Industry-Standard Ultra Fast Dual Comparator (10KH ECL)             |

| Bt688 | Wide Input Voltage Dual Comparator (10KH ECL)                       |

| Bt689 | Programmable Pin Electronics Driver/Load (10KH ECL)                 |

| Bt698 | Programmable Pin Electronics Driver and Comparator (10KH ECL)9 - 57 |

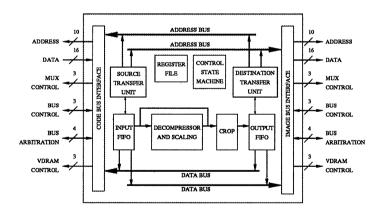

| Bt701 | Image Decompression Accelerator                                     |

# **Brooktree**<sup>®</sup>

**Imaging/Graphics**

Introduction

**Quality Assurance**

**Product Index**

## VIDEODACs

**RAMDACs**

Peripherals

**Imaging Products**

**Application Notes**

Automatic Test Equipment

**Military**

Timing/Comparators/ Drivers/Loads

**Data Conversion**

Military 883C Products

**Packaging Information**

Sales Offices

## **Table of Contents**

| Bt101 | 50, 30 MHz Triple 8-bit VIDEODAC                                                   |

|-------|------------------------------------------------------------------------------------|

| Bt102 | 75 MHz Single 8-bit VIDEODAC with Programmable Setup                               |

| Bt103 | 75, 30 MHz Triple 4-bit VIDEODAC                                                   |

| Bt106 | 50, 30 MHz Single 8-bit VIDEODAC                                                   |

| Bt107 | 400 MHz Single 8-bit VIDEODAC with 2:1 Multiplexed Pixel Inputs<br>(10KH/100K ECL) |

| Bt109 | 250 MHz Triple 8-bit VIDEODAC, TDC1318 Pin Compatible(10KH ECL)                    |

| D/A<br>Organization | Speed (MHz) | Part<br>Number | Page   | DL Error<br>(LSB) | IL Error<br>(LSB) |                          |

|---------------------|-------------|----------------|--------|-------------------|-------------------|--------------------------|

| triple 4-bit        | 75, 30      | Bt103          | 4 - 33 | ± 1/16            | ± 1/8             | monolithic CMOS          |

| single 8-bit        | 400         | Bt107          | 4 - 61 | ± 1/2             | ± 1/2             | 2:1 muxed inputs         |

| single 8-bit        | 75          | Bt102          | 4 - 19 | ± 1/4             | ± 1/2             | programmable setup       |

| single 8-bit        | 50, 30      | Bt106          | 4 - 47 | ± 1               | ± 1               | monolithic CMOS          |

| triple 8-bit        | 250         | Bt109          | 4 - 75 | ± 1/2             | ± 1/2             | 10KH ECL monolithic CMOS |

| triple 8-bit        | 50, 30      | Bt101          | 4 - 5  | ± 1               | ± 1               |                          |

## **VIDEODAC** Selection Guide

|          | Display Resolution      |                      |                       |                              |                         |  |  |

|----------|-------------------------|----------------------|-----------------------|------------------------------|-------------------------|--|--|

| DAC Size | Low<br>(640 x 480)      | Medium<br>(1k x 800) | High<br>(1280 x 1024) | Medium High<br>(1600 x 1200) | Ultra High<br>(2k x 2k) |  |  |

| 4-bit    | Bt103                   | Bt103                |                       |                              |                         |  |  |

| 8-bit    | Bt101<br>Bt102<br>Bt106 | Bt102                | B1109                 | Bt109                        | Bt107                   |  |  |

4

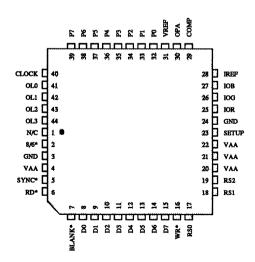

# Bt101

## 50 MHz

**Monolithic CMOS**

**Triple 8-bit**

## **VIDEODAC**<sup>™</sup>

### **Distinguishing Features**

- 50, 30 MHz Operation

- Triple 8-bit D/A Converters

- ± 1 LSB Differential Linearity Error

- ± 1 LSB Integral Linearity Error

- Guaranteed Monotonic

- RS-343A/RS-170 Compatible Outputs

- TTL Compatible Inputs

- +5v CMOS Monolithic Construction

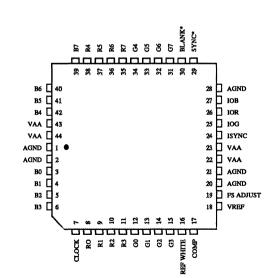

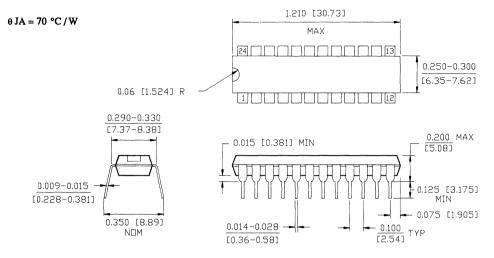

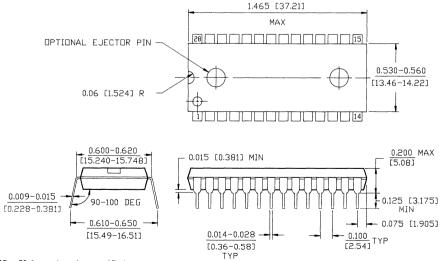

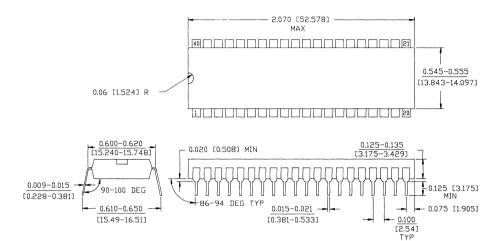

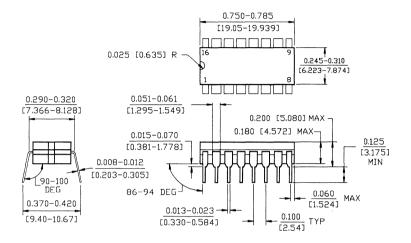

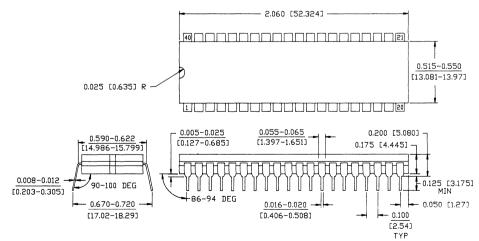

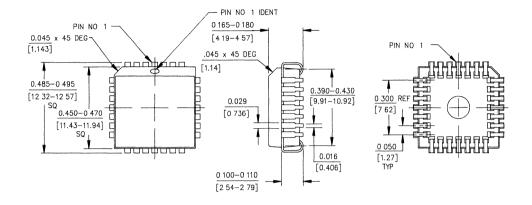

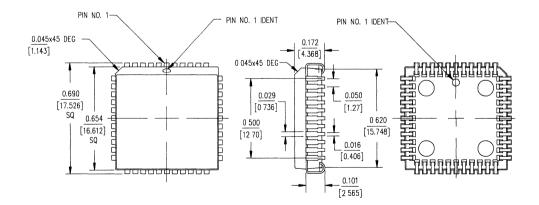

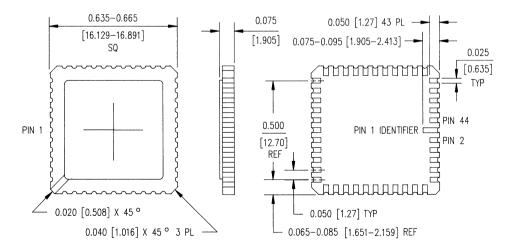

- 40-pin DIP or 44-pin PLCC Package

- Typical Power Dissipation: 600 mW

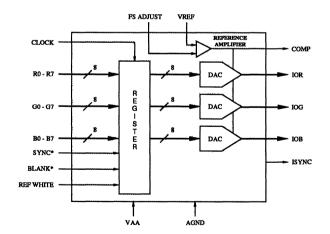

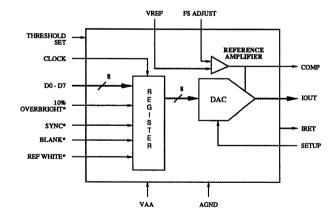

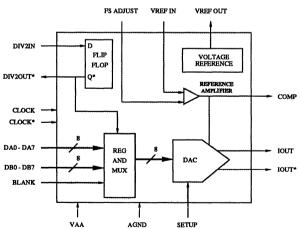

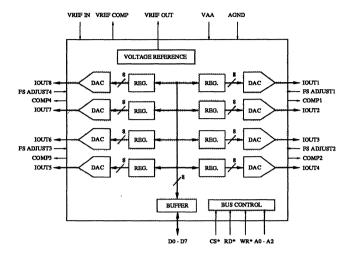

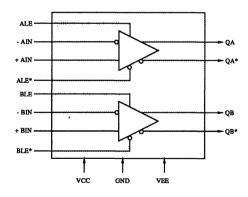

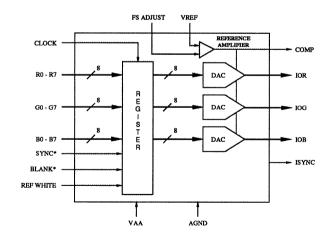

## **Functional Block Diagram**

Brooktree Corporation 9950 Barnes Canyon Rd. San Diego, CA 92121 (619) 452-7580 (800) VIDEO IC TLX: 383 596 FAX: (619) 452-1249 L101001 Rev. H

### Applications

- High Resolution Color Graphics

- CAE/CAD/CAM Applications

- Image Processing

- Video Reconstruction

- Instrumentation

### **Product Description**

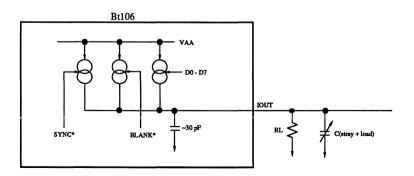

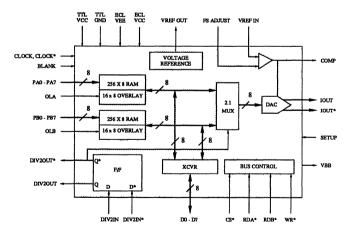

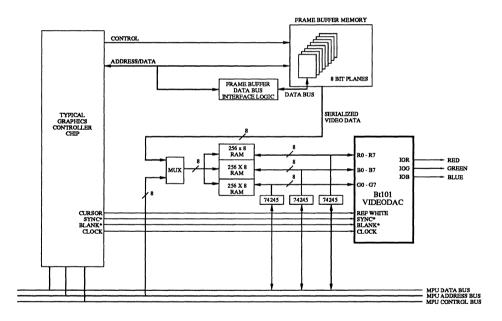

The Bt101 is a triple 8-bit VIDEODAC, designed specifically for high performance, high resolution color graphics.

Available control inputs include sync, blank, and reference white. The reference white input forces the analog outputs to the reference white level, regardless of the data inputs.

An external 1.2v voltage reference and a single resistor control the full scale output current. The sync, blank, and reference white inputs are pipelined to maintain synchronization with the digital input data.

The Bt101 generates RS-343A compatible video signals into a doubly-terminated 75-ohm load, and RS-170 compatible video signals into a singly-terminated 75-ohm load, without requiring external buffering. Both the differential and integral linearity errors of the D/A converters are guaranteed to be a maximum of  $\pm 1$  LSB over the full temperature range.

# **Brooktree**<sup>®</sup>

#### **Circuit Description**

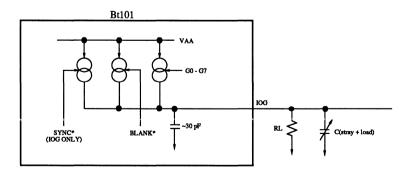

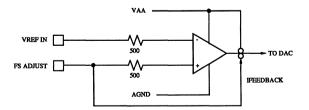

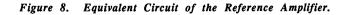

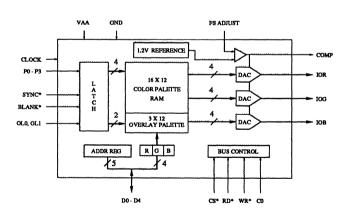

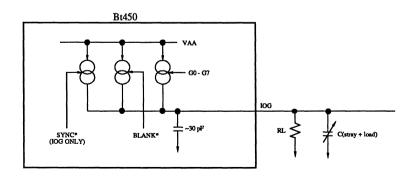

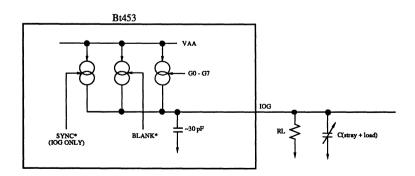

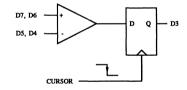

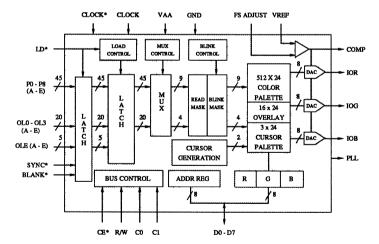

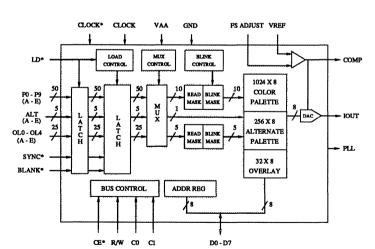

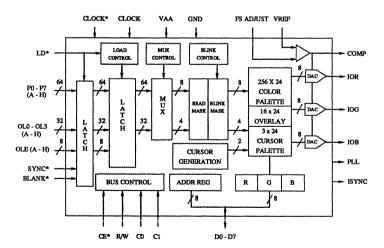

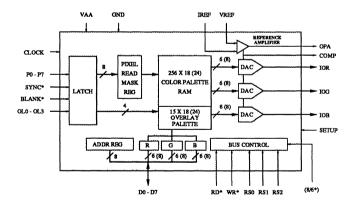

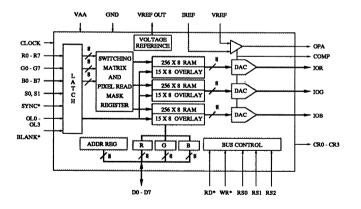

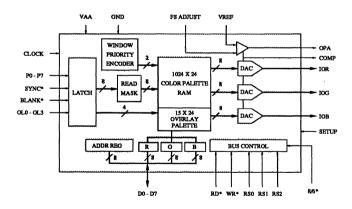

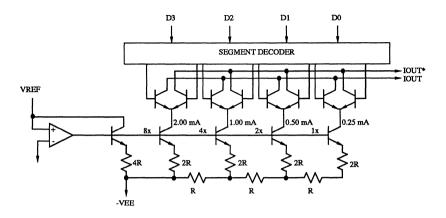

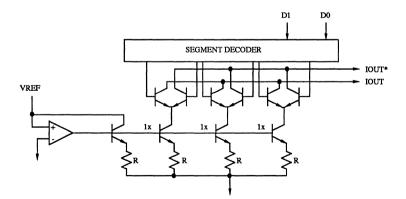

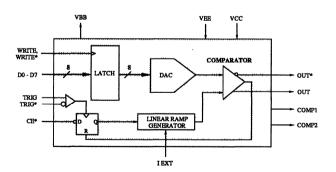

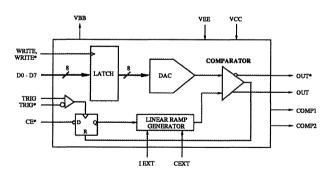

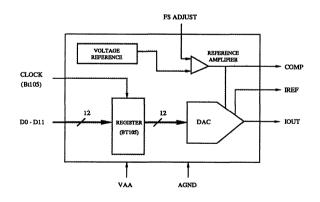

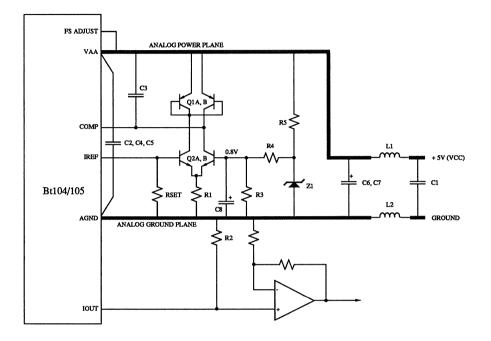

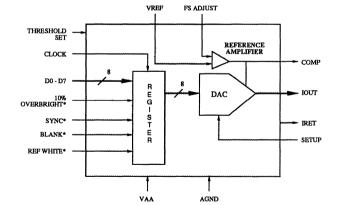

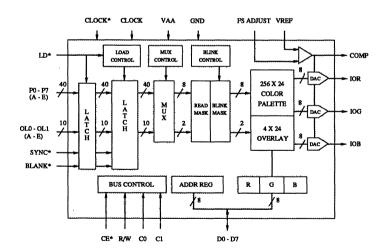

As illustrated in the functional block diagram, the Bt101 contains three 8-bit D/A converters, input registers, and a reference amplifier.

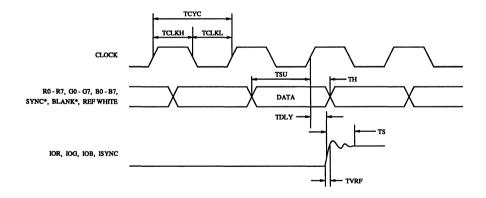

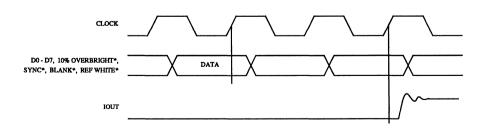

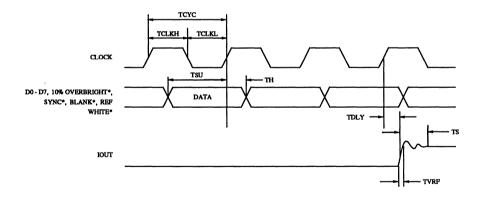

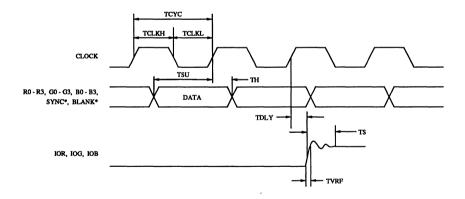

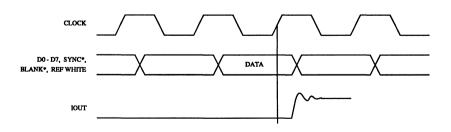

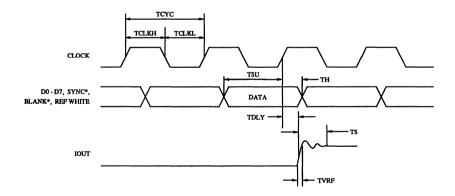

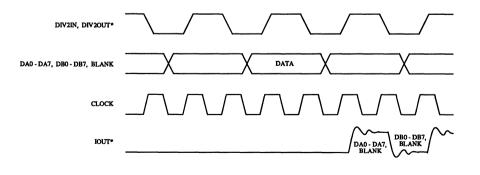

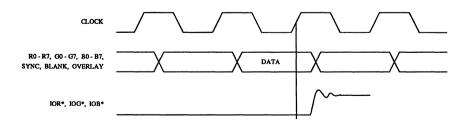

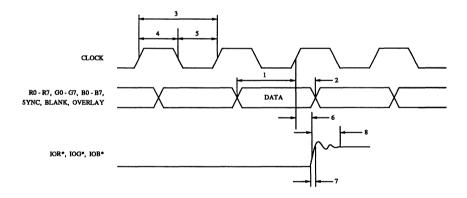

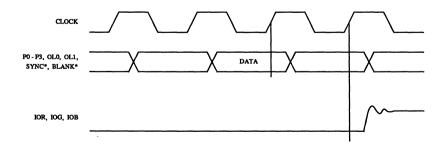

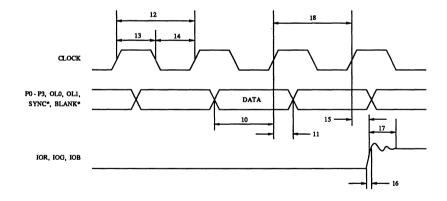

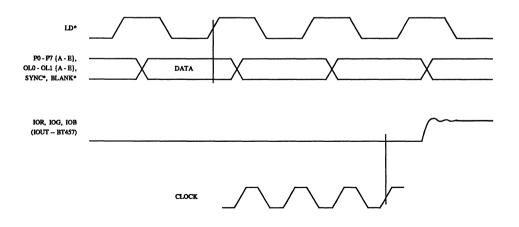

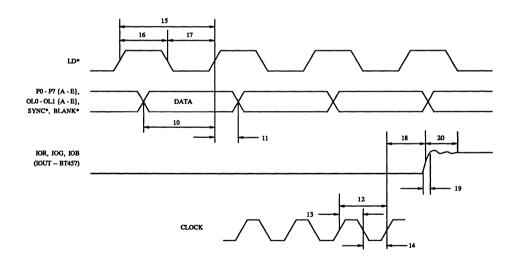

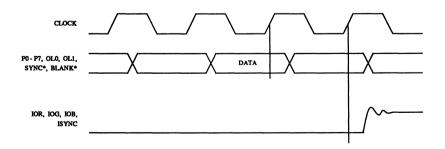

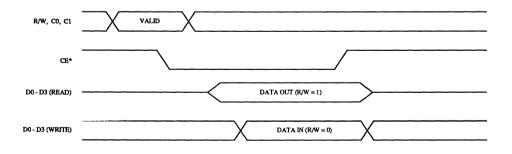

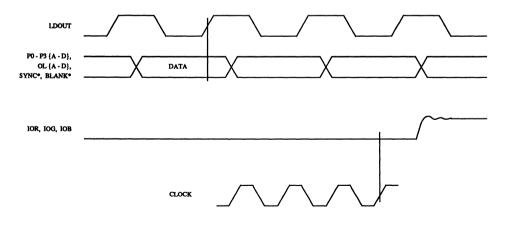

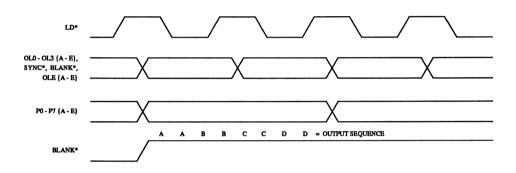

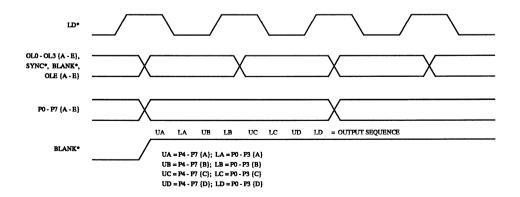

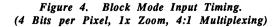

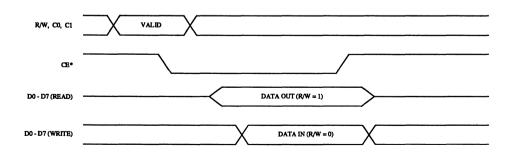

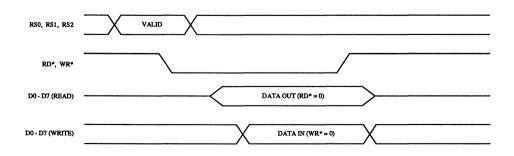

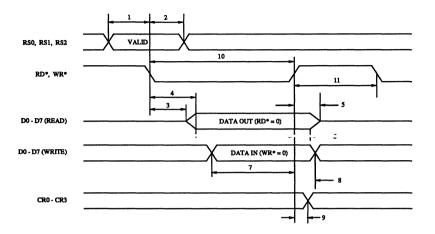

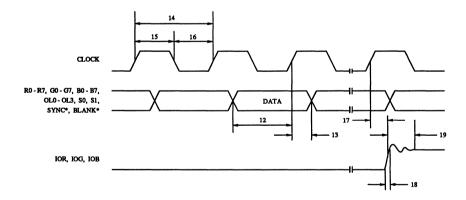

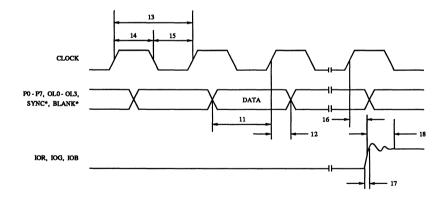

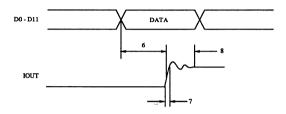

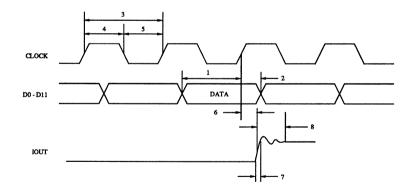

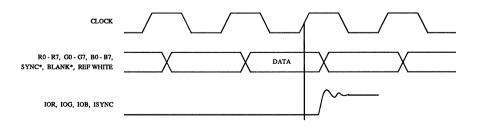

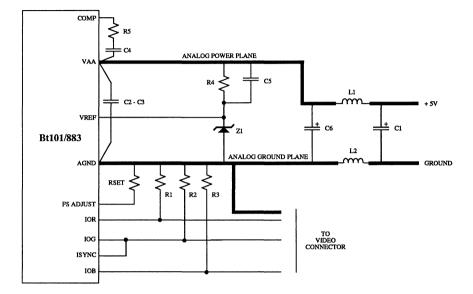

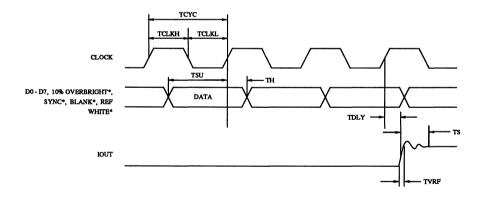

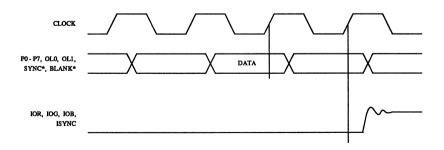

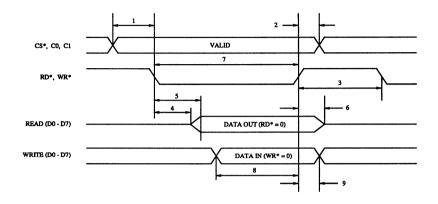

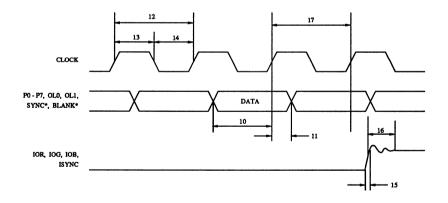

On the rising edge of each clock cycle, as shown below in Figure 1, 24 bits of color information (R0 - R7, G0 - G7, and B0 - B7) are latched into the device and presented to the three 8-bit D/A converters. The REF WHITE input, also latched on the rising edge of each clock cycle, forces the inputs of each D/A converter to FF.

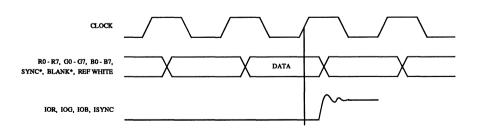

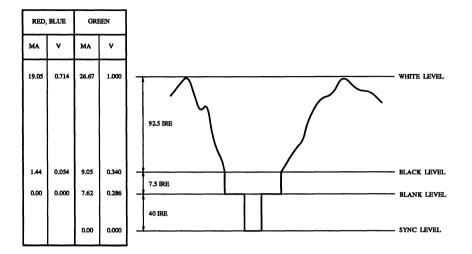

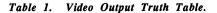

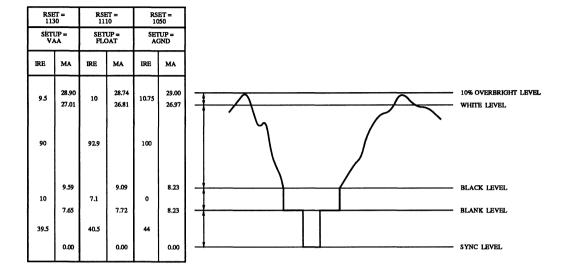

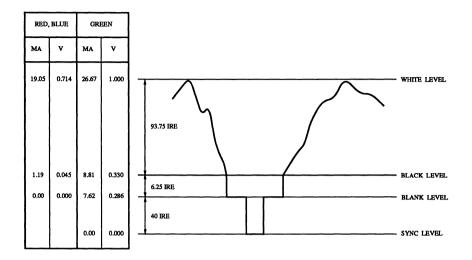

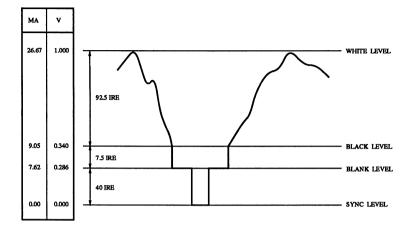

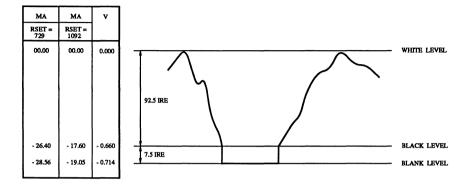

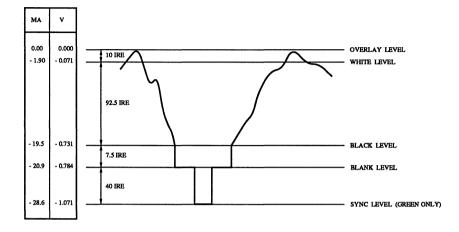

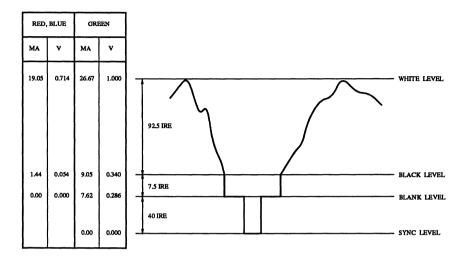

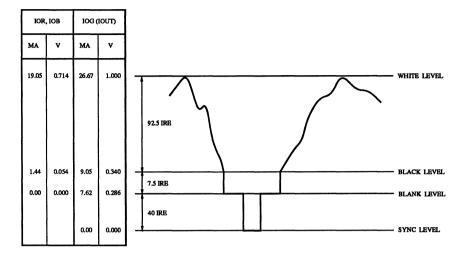

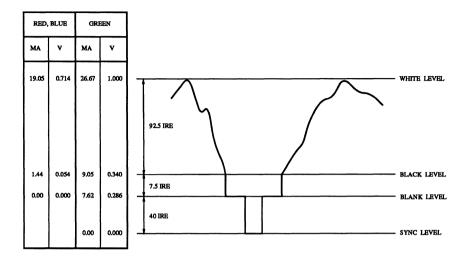

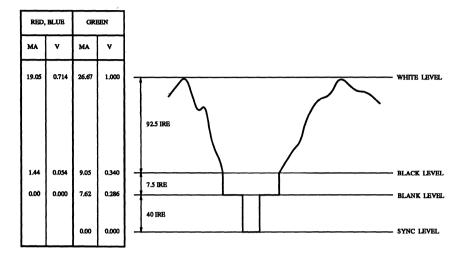

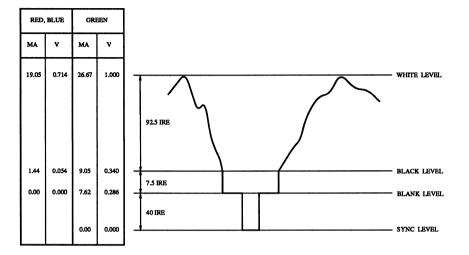

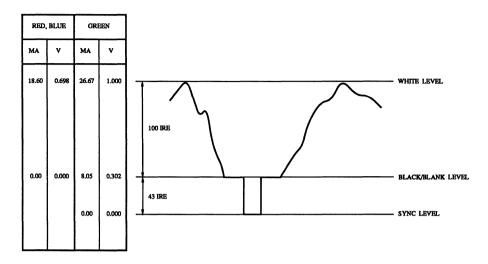

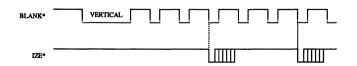

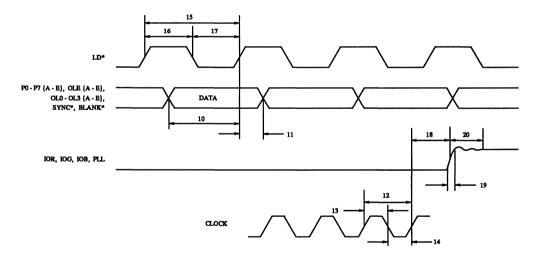

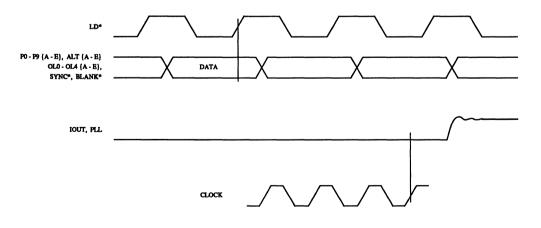

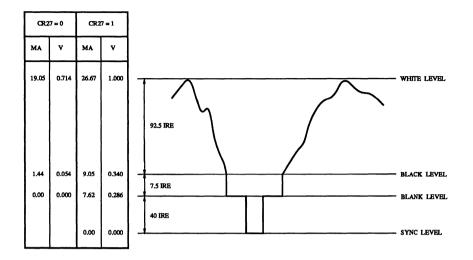

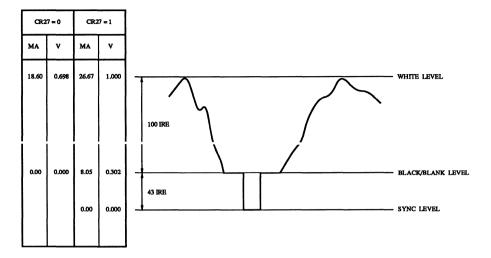

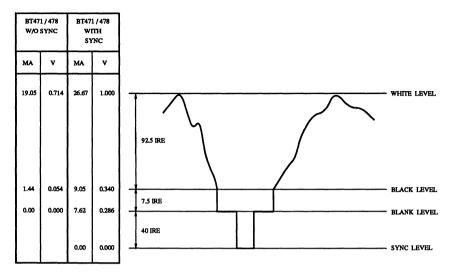

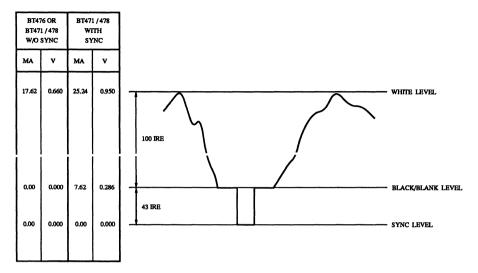

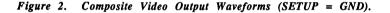

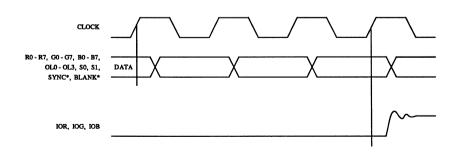

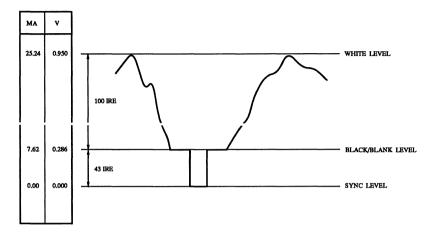

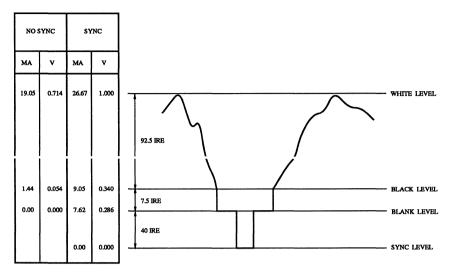

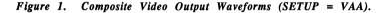

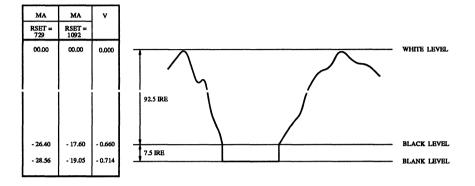

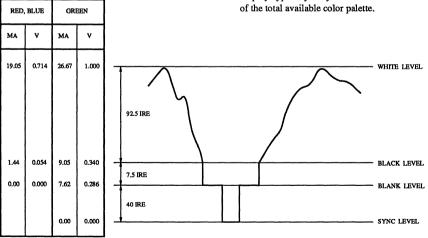

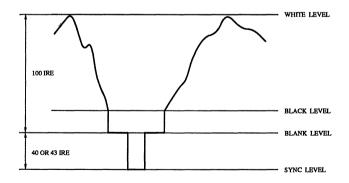

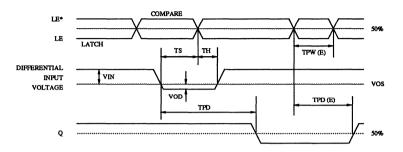

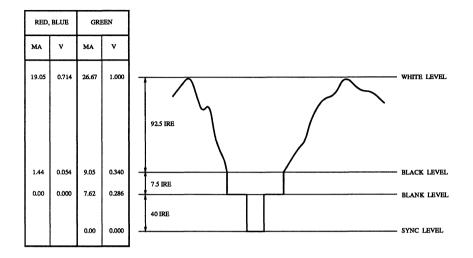

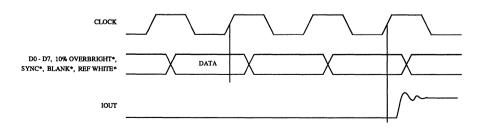

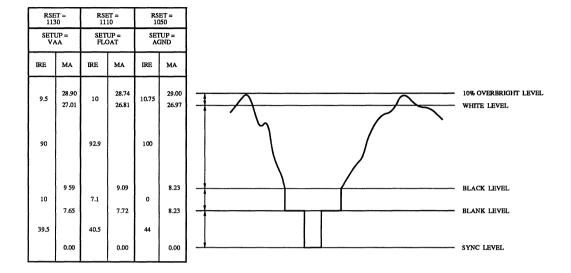

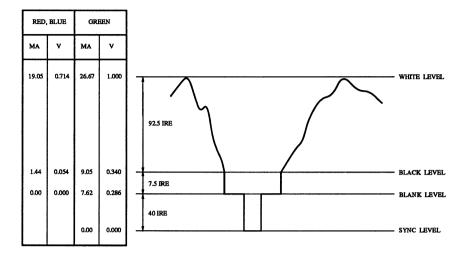

Latched on the rising edge of CLOCK to maintain synchronization with the color data, the SYNC\* and BLANK\* inputs add appropriately weighted currents to the analog outputs, producing the specific output levels required for video applications as illustrated in Figure 2. Table 1 details how the SYNC\*, BLANK\*, and REF WHITE inputs modify the output levels.

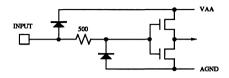

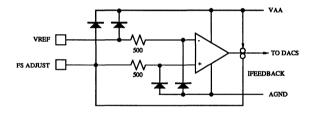

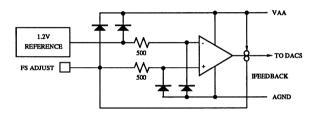

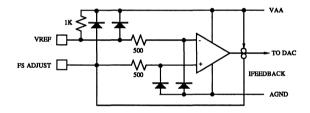

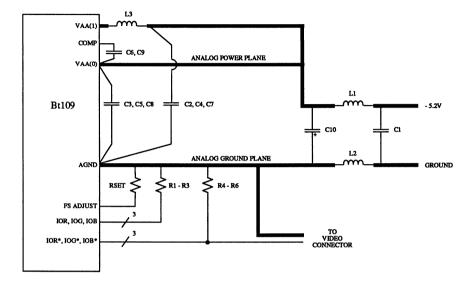

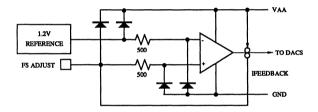

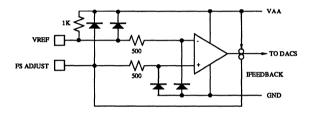

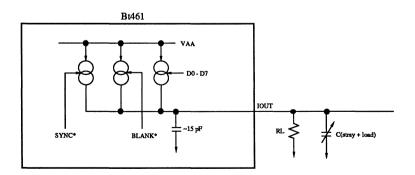

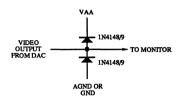

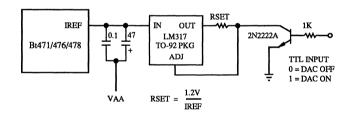

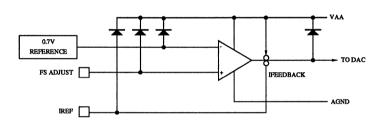

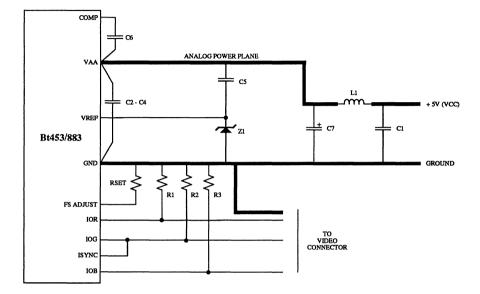

The ISYNC current output is typically connected directly to the IOG output and is used to encode sync information onto the IOG output. If ISYNC is not connected to the IOG output, sync information will not be encoded on the green channel, and the IOR, IOG, and IOB outputs will have the same full scale output current. Full scale output current is set by an external resistor (RSET) between the FS ADJUST pin and AGND. RSET has a typical value of 542 ohms for generation of RS-343A video into a 37.5-ohm load. The VREF input requires an external 1.2v (typical) reference. For maximum performance, the voltage reference should be temperature compensated and provide a low-impedance output.

The D/A converters on the Bt101 use a segmented architecture in which bit currents are routed to either the output or AGND by a sophisticated decoding scheme. This architecture eliminates the need for precision component ratios and greatly reduces the switching transients associated with turning current sources on or off. Monotonicity and low glitch are guaranteed by using identical current sources and current steering their outputs. An on-chip operational amplifier stabilizes the full-scale output current against temperature and power supply variations.

The analog outputs of the Bt101 are capable of directly driving a 37.5-ohm load, such as a doubly-terminated 75-ohm coaxial cable.

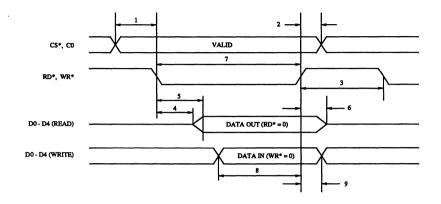

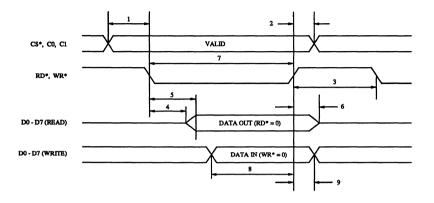

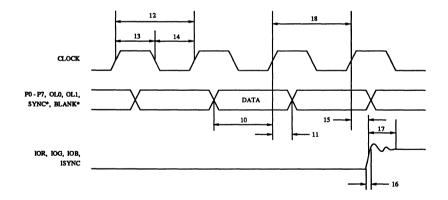

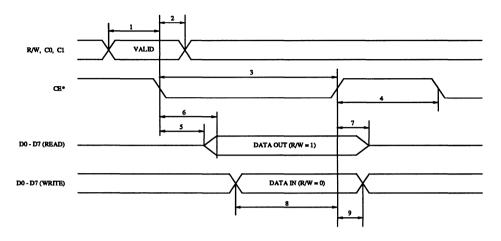

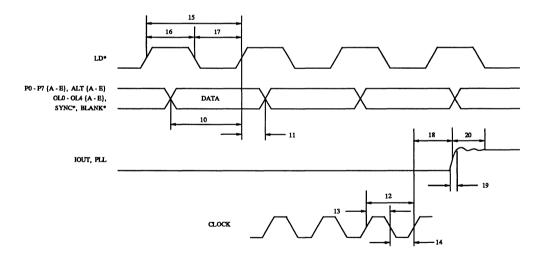

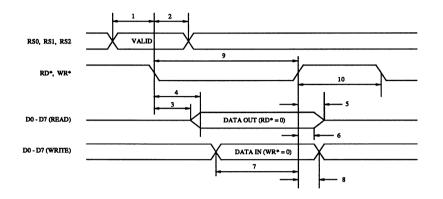

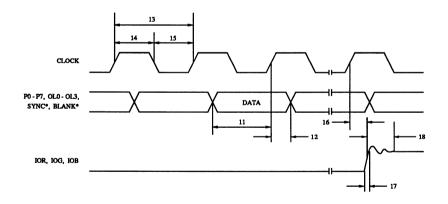

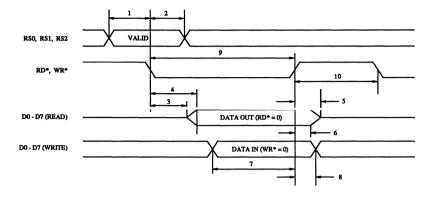

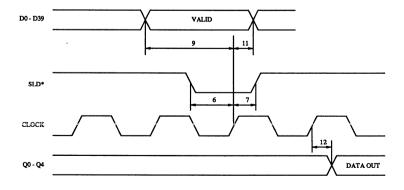

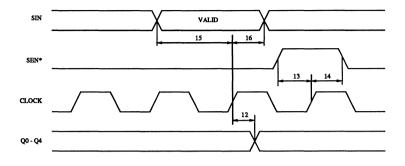

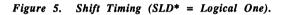

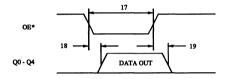

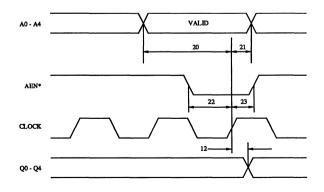

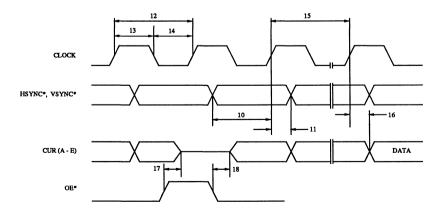

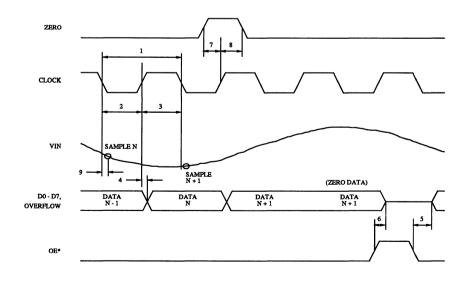

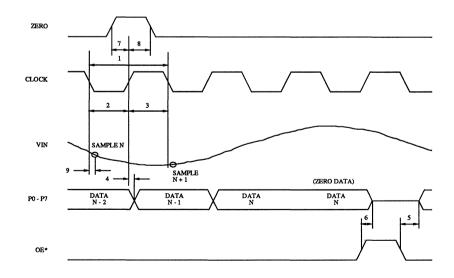

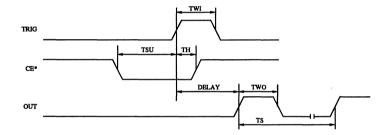

Figure 1. Input/Output Timing.

## **Circuit Description (continued)**

Note: 75-ohm doubly-terminated load, RSET = 542 ohms, VREF = 1.2v. ISYNC connected to IOG. RS-343A levels and tolerances assumed on all levels.

| Description  | IOG<br>(mA) | IOR, IOB<br>(mA) | REF<br>WHITE | SYNC* | BLANK* | DAC<br>Input Data |

|--------------|-------------|------------------|--------------|-------|--------|-------------------|

| WHITE        | 26.67       | 19.05            | 1            | 1     | 1      | \$xx              |

| WHITE        | 26.67       | 19.05            | 0            | 1     | 1      | \$FF              |

| DATA         | data + 9.05 | data + 1.44      | 0            | 1     | 1      | data              |

| DATA - SYNC  | data + 1.44 | data + 1.44      | 0            | 0     | 1      | data              |

| BLACK        | 9.05        | 1.44             | 0            | 1     | 1      | \$00              |

| BLACK - SYNC | 1.44        | 1.44             | 0            | 0     | 1      | \$00              |

| BLANK        | 7.62        | 0                | x            | 1     | 0      | \$xx              |

| SYNC         | 0           | 0                | x            | 0     | 0      | \$xx              |

Note: Typical with full scale IOG = 26.67 mA. RSET = 542 ohms, VREF = 1.2v. ISYNC connected to IOG.

4

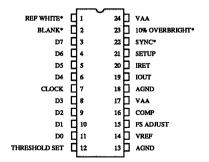

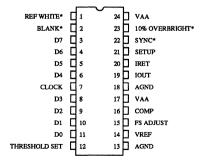

## **Pin Descriptions**

| Pin Name                        | Description                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLANK*                          | Composite blank control input (TTL compatible). A logical zero drives the IOR, IOG, and IOB outputs to the blanking level, as illustrated in Table 1. It is latched on the rising edge of CLOCK. When BLANK* is a logical zero, the R0 - R7, G0 - G7, B0 - B7, and REF WHITE inputs are ignored.                                                  |

| SYNC*                           | Composite sync control input (TTL compatible). A logical zero on this input switches off a 40 IRE current source on the ISYNC output (see Figure 2). SYNC* does not override any other control or data input, as shown in Table 1; therefore, it should be asserted only during the blanking interval. It is latched on the rising edge of CLOCK. |

| REF WHITE                       | Reference white control input (TTL compatible). A logical one on this input forces the IOR, IOG, and IOB outputs to the white level, regardless of the R0 - R7, G0 - G7, and B0 - B7 inputs. It is latched on the rising edge of CLOCK. See Table 1.                                                                                              |

| R0 - R7,<br>G0 - G7,<br>B0 - B7 | Red, green, and blue data inputs (TTL compatible). R0, G0, and B0 are the least significant data bits. They are latched on the rising edge of CLOCK. Coding is binary. Unused inputs should be connected to either the regular PCB power or ground plane.                                                                                         |

| CLOCK                           | Clock input (TTL compatible). The rising edge of CLOCK latches the R0 - R7, G0 - G7, B0 - B7, SYNC*, BLANK*, and REF WHITE inputs. It is typically the pixel clock rate of the video system. It is recommended that the CLOCK input be driven by a dedicated TTL buffer.                                                                          |

| IOR, IOG, IOB                   | Red, green, and blue current outputs. These high impedance current sources are capable of directly driving a doubly-terminated 75-ohm coaxial cable (Figure 3). All outputs, whether used or not, should have the same output load.                                                                                                               |

| ISYNC                           | Sync current output. Typically, this current output is directly wired to the IOG output, and enables sync information to be encoded onto the green channel. A logical zero on the SYNC* input results in no current being output onto this pin, while a logical one results in the following current being output:                                |

|                                 | ISYNC (mA) = 3,442 * VREF (v) / RSET (ohms)                                                                                                                                                                                                                                                                                                       |

|                                 | If sync information is not required on the green channel, this output should be connected to AGND.                                                                                                                                                                                                                                                |

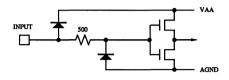

| FS ADJUST                       | Full scale adjust control. A resistor (RSET) connected between this pin and AGND controls the magnitude of the full scale video signal (Figure 2). Note that the IRE relationships in Figure 2 are maintained, regardless of the full scale output current.                                                                                       |

|                                 | The relationship between RSET and the full scale output current on IOG (assuming ISYNC is connected to IOG) is:                                                                                                                                                                                                                                   |

|                                 | RSET (ohms) = 12,046 * VREF (v) / IOG (mA)                                                                                                                                                                                                                                                                                                        |

|                                 | The full scale output current on IOR and IOB for a given RSET is defined as:                                                                                                                                                                                                                                                                      |

|                                 | IOR, IOB (mA) = $8,604 * VREF (v) / RSET (ohms)$                                                                                                                                                                                                                                                                                                  |

|                                 |                                                                                                                                                                                                                                                                                                                                                   |

## Pin Descriptions (continued)

| Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

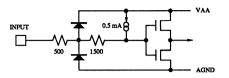

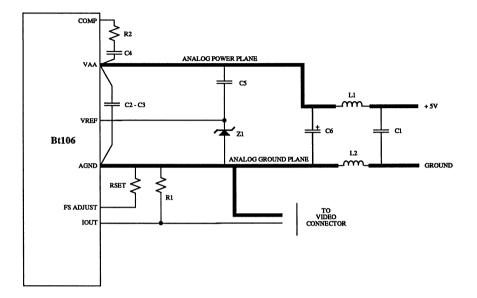

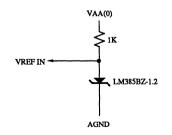

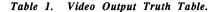

| COMP     | Compensation pin. This pin provides compensation for the internal reference amplifier. A 0.01 $\mu$ F ceramic capacitor in series with a resistor must be connected between this pin and the nearest VAA pin (Figure 3). Connecting the capacitor to VAA rather than to AGND provides the highest possible power supply noise rejection. The COMP resistor and capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum.                                                                                            |

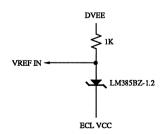

| VREF     | Voltage reference input. An external voltage reference circuit, such as the one shown in Figure 3, must supply this input with a 1.2v (typical) reference. The use of a resistor network to generate the reference is not recommended, as any low frequency power supply noise on VREF will be directly coupled onto the analog outputs. A 0.1 $\mu$ F ceramic capacitor must be used to decouple this input to VAA, as shown in Figure 3. The decoupling capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum. |

| AGND     | Analog ground. All AGND pins must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VAA      | Analog power. All VAA pins must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

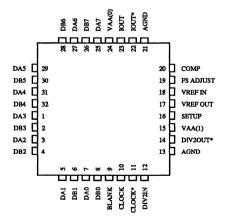

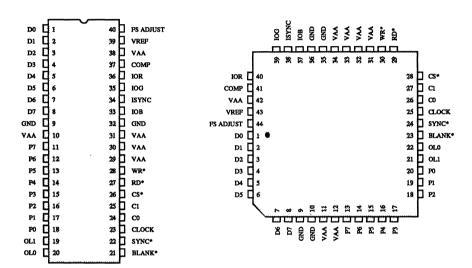

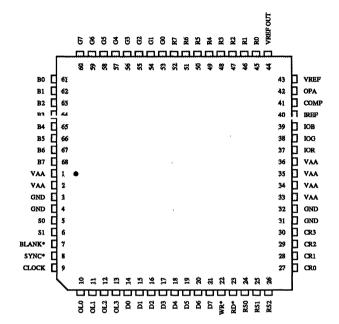

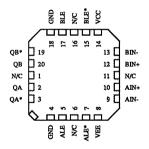

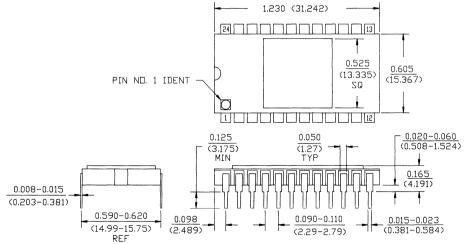

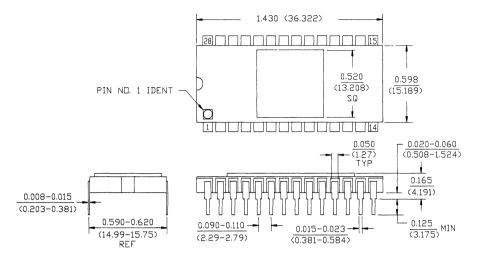

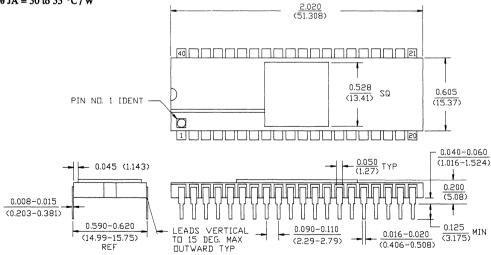

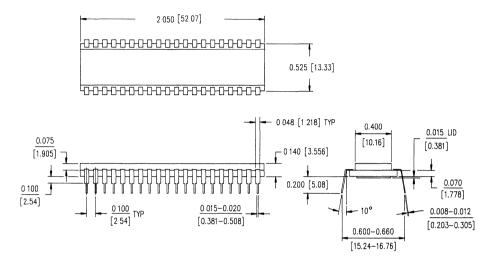

40-pin DIP Package

G4 [] 1 R7 [] 2

D

d R4 5

Ľ٩ **B4**

**[** 10

R6 3

R5 4

**B**7 ٥ 6

**B6** П 7

B5 8

VAA

AGND 11

B0 12

B1 🛛 13

B2 🚺 14

B3 115

R0 17

R1 [] 18 R2 [] 19

R3 20

стоск [ те

44-pin Plastic J-Lead (PLCC) Package

BLANK\* 36 SYNC\* 35 AGND

40 🗋 GS 39 🛛 G6

38 67

37

ж□ IOB

33 🗋 IOR

32 🗍 10G

31 ISYNC

30 🗍 VAA

29 AGND

27 VREF

26 COMP

24 🗍 G3

23 0 62

22 GI

21 00

28 FS ADJUST

25 REF WHITE

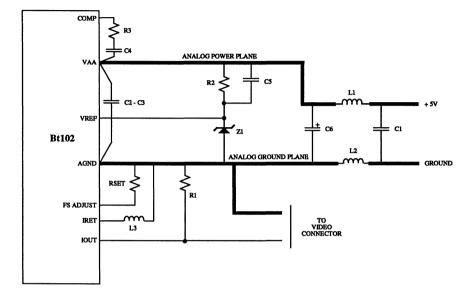

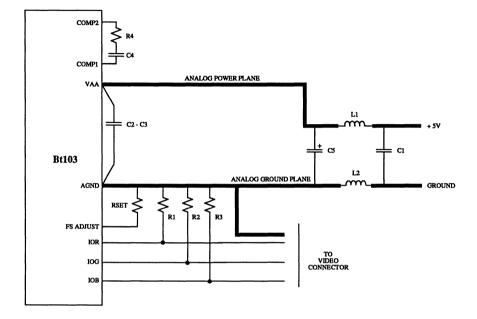

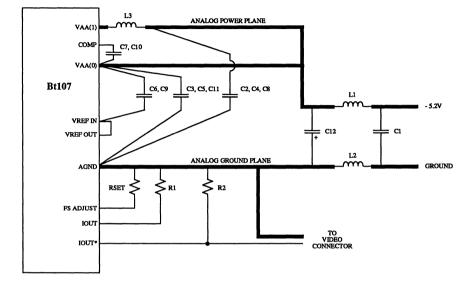

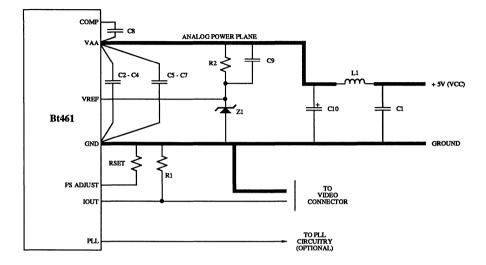

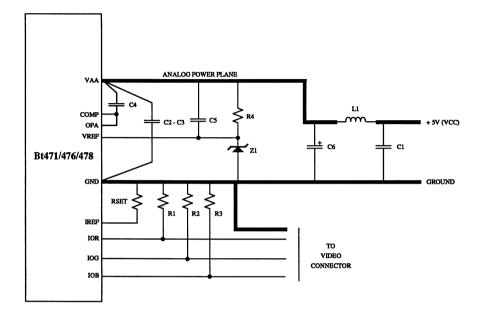

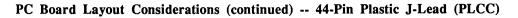

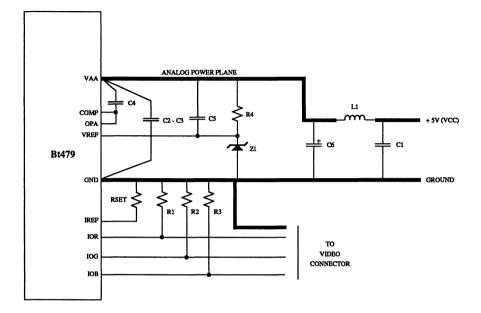

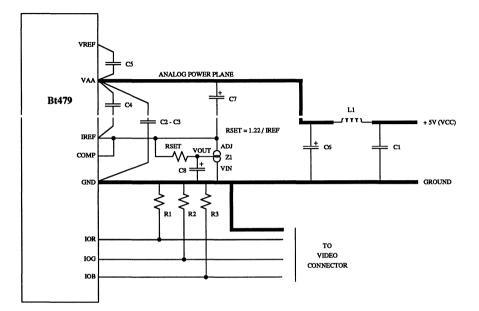

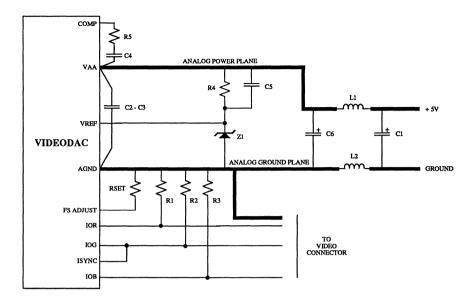

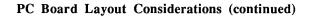

## PC Board Layout Considerations

#### PC Board Considerations

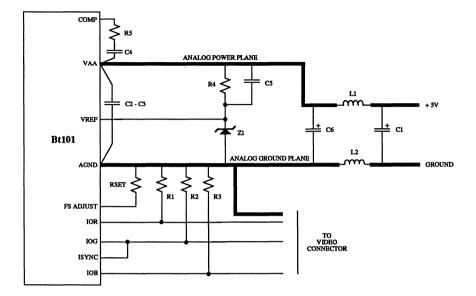

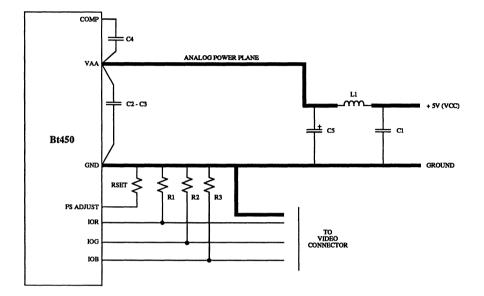

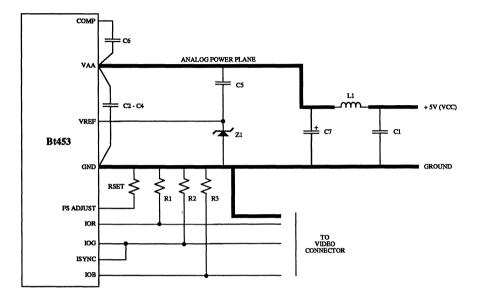

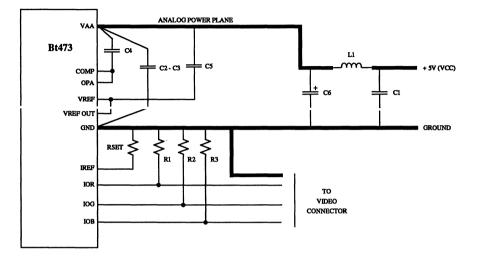

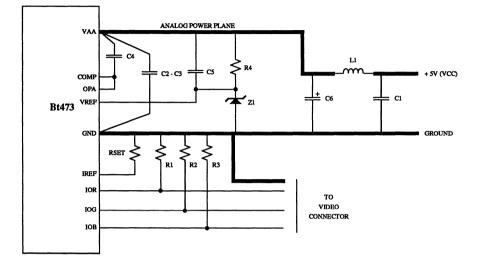

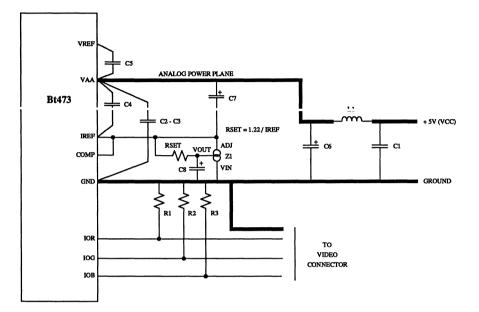

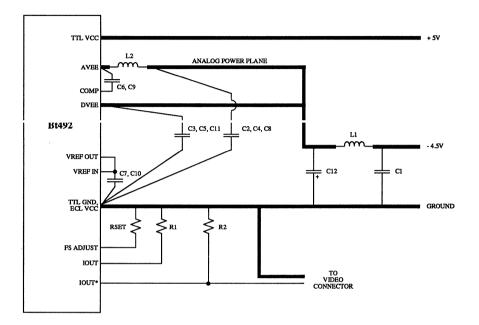

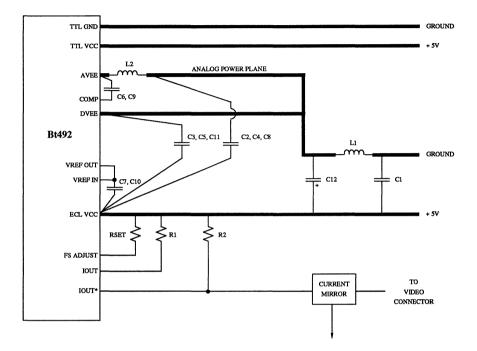

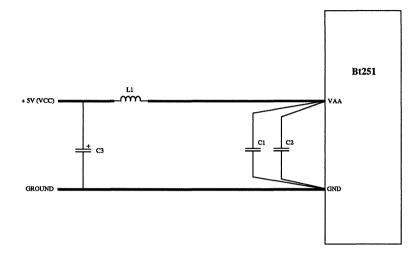

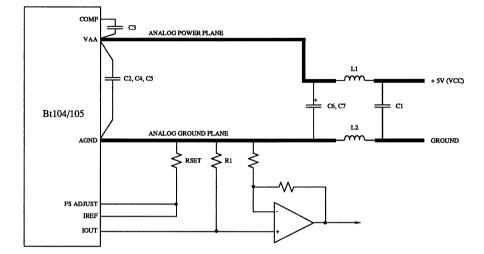

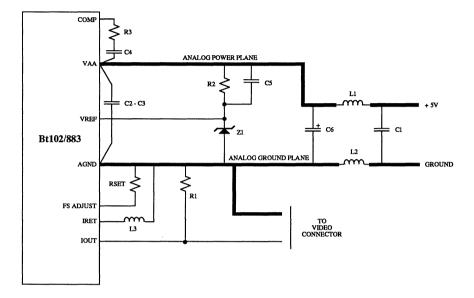

The layout should be optimized for lowest noise on the Bt101 power and ground lines by shielding the digital inputs and providing good decoupling. The lead length between groups of VAA and AGND pins should be minimized so as to minimize inductive ringing.

#### Ground Planes

The Bt101 and any associated analog circuitry should have its own ground plane, referred to as the analog ground plane. This ground plane should connect to the regular PCB ground plane at a single point through a ferrite bead, as illustrated in Figure 3. This bead should be located within three inches of the Bt101.

The analog ground plane area should encompass all Bt101 ground pins, voltage reference circuitry, power supply bypass circuitry for the Bt101, the analog output traces, and any output amplifiers.

The regular PCB ground plane area should encompass all the digital signal traces, excluding the ground pins, leading up to the Bt101.

#### Power Planes

The Bt101 and any associated analog circuitry should have its own power plane, referred to as the analog power plane. This power plane should be connected to the regular PCB power plane at a single point through a ferrite bead, as illustrated in Figure 3. This bead should be located within three inches of the Bt101.

The PCB power plane should provide power to all digital logic on the PC board, and the analog power plane should provide power to all Bt101 power pins, voltage reference circuitry, and any output amplifiers.

It is important that portions of the regular PCB power and ground planes do not overlay portions of the analog power or ground planes, unless they can be arranged such that the plane-to-plane noise is common mode. This will reduce plane-to-plane noise coupling.

#### Supply Decoupling

The bypass capacitors should be installed using the shortest leads possible, consistent with reliable operation, to reduce the lead inductance.

For the best performance, a 0.1  $\mu$ F ceramic capacitor should be used to decouple each of the two groups of VAA pins to AGND. These capacitors should be placed as close as possible to the device.

It is important to note that while the Bt101 contains circuitry to reject power supply noise, this rejection decreases with frequency. If a switching power supply is used, the designer should pay close attention to reducing power supply noise and consider using a three terminal voltage regulator for supplying power to the analog power plane.

#### Digital Signal Interconnect

The digital inputs to the Bt101 should be isolated as much as possible from the analog outputs and other analog circuitry. Also, these input signals should not overlay the analog ground and power planes.

Due to the high clock rates involved, long clock lines to the Bt101 should be avoided to reduce noise pickup.

Any active termination resistors for the digital inputs should be connected to the regular PCB power and ground planes.

#### Analog Signal Interconnect

The Bt101 should be located as close as possible to the output connectors to minimize noise pickup and reflections due to impedance mismatch.

The video output signals should overlay the analog ground plane, and not the analog power plane, to maximize the high frequency power supply rejection.

For maximum performance, the analog outputs should each have a 75-ohm load resistor connected to AGND. The connection between the current output and AGND should be as close as possible to the Bt101 to minimize reflections.

## **Brooktree**®

## PC Board Layout Considerations (continued)

| Location                                                                       | Description                                                                                                                                                                                                                                                                                                                                                              | Vendor Part Number                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1<br>C2, C3, C5<br>C4<br>C6<br>L1, L2<br>R1, R2, R3<br>R4<br>R5<br>RSET<br>Z1 | <ul> <li>33 μF tantalum capacitor</li> <li>0.1 μF ceramic capacitor</li> <li>0.01 μF ceramic capacitor</li> <li>10 μF tantalum capacitor</li> <li>ferrite bead</li> <li>75-ohm 1% metal film resistor</li> <li>1000-ohm 1% metal film resistor</li> <li>15-ohm 1% metal film resistor</li> <li>549-ohm 1% metal film resistor</li> <li>1.2v voltage reference</li> </ul> | Mallory CSR13F336KM<br>Erie RPE112Z5U104M50V<br>Erie RPE110Z5U103M50V<br>Mallory CSR13G106KM<br>Fair-Rite 2743001111<br>Dale CMF-55C<br>Dale CMF-55C<br>Dale CMF-55C<br>Dale CMF-55C<br>National Semiconductor LM385BZ-1.2 |

Note: The above listed vendor numbers are listed only as a guide. Substitution of devices with similar characteristics will not affect the performance of the Bt101.

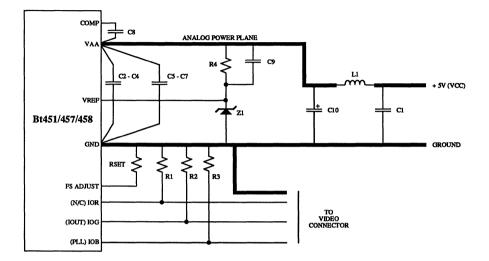

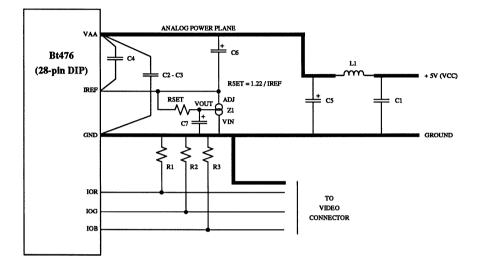

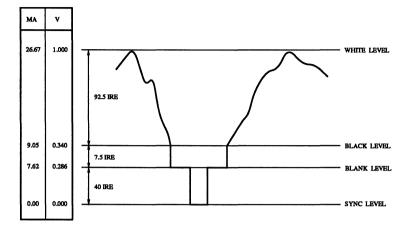

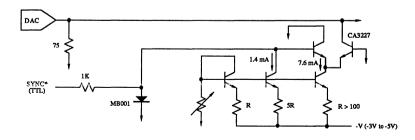

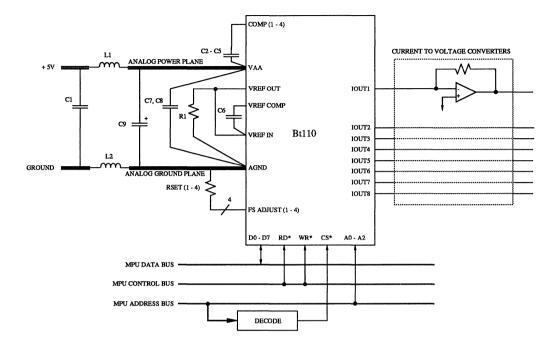

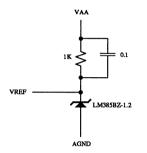

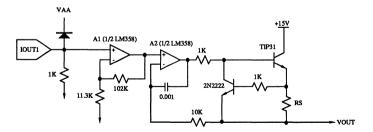

#### Figure 3. Typical Connection Diagram and Parts List.

## **Application Information**

#### **RS-170 Video Generation**

For generation of RS-170 compatible video, it is recommended that a singly-terminated 75-ohm load be used with an RSET value of about 774 ohms. If the Bt101 is not driving a large capacitive load, there will be negligible difference in video quality between doubly-terminated 75-ohm and singly-terminated 75-ohm loads.

If driving a large capacitive load (load  $RC > 1/(20Fc\pi)$ ), it is recommended that an output buffer be used to drive a doubly-terminated 75-ohm load.

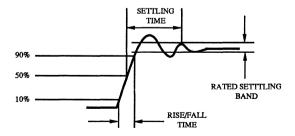

#### COMP Resistor

To optimize the settling time of the Bt101, a resistor may be added in series between the COMP capacitor and COMP pin. The series resistor damps inductive ringing on COMP, thus improving settling time.

The value of the resistor is typically 15 ohms, however, the exact value is dependent on the PC board layout, clock rate, etc., and should be optimized for minimal settling time.

An incorrect resistor value will result in degraded output performance, such as excessive ringing of the analog outputs or increased settling time.

#### Non-Video Applications

The Bt101 may be used in non-video applications by disabling the video-specific control inputs. SYNC\* and REF WHITE should be a logical zero and BLANK\* should be a logical one. ISYNC should be connected to AGND. All three outputs will have the same full scale output current.

The relationship between RSET and the full scale output current (Iout) in this configuration is as follows:

RSET (ohms) = 7,958 \* VREF (v) / Iout (mA)

With the data inputs at \$00, there is a DC offset current (Imin) defined as follows:

Imin(mA) = 650 \* VREF(v) / RSET(ohms)

Therefore, the total full scale output current will be Iout + Imin. The REF WHITE input may optionally be used as a "force to full scale" control.

## **Recommended Operating Conditions**

| Parameter                                                                       | Symbol             | Min               | Тур                 | Max                  | Units                 |

|---------------------------------------------------------------------------------|--------------------|-------------------|---------------------|----------------------|-----------------------|

| Power Supply<br>Ambient Operating Temperature<br>Bt101KC30, Bt101KPJ<br>Bt101BC | VAA<br>TA          | 4.75<br>0<br>- 25 | 5.00                | 5.25<br>+ 70<br>+ 85 | Volts<br>°C.<br>°C.   |

| Output Load<br>Reference Voltage<br>FS ADJUST Resistor                          | RL<br>VREF<br>RSET | - 25              | 37.5<br>1.20<br>542 | 1.26                 | Ohms<br>Volts<br>Ohms |

## **Absolute Maximum Ratings**

| Parameter                                                                                                          | Symbol         | Min          | Тур        | Max                              | Units             |

|--------------------------------------------------------------------------------------------------------------------|----------------|--------------|------------|----------------------------------|-------------------|